[ompuPro"

-6

10 mg On

-

-.

0 0 5.0

.

-

-0

0 1

0 000

0.0

-- 61

-

()

-

.

0 0

-

0\_0

8 8

0 0

-

à

0.0 000

-

-

-02

-

ė

-0.0 -05

OFPP

\$20.00

HIGH PERFORMANCE Z80 64 or 256K RAM DUAL ASYNCHRONOUS COMMUNICATION CHANNELS SPUZ TECHNICAL MANUAL Copyright 1985 Viasyn Corporation Hayward, CA 94545

First Edition: April, 1985 Latest Printing: July, 1985

Part No. 8261-0030 Filename: SPUZNEW.MAN Board No: 257E

**DISCLAIMER** - Viasyn Corporation makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantablity or fitness for any particular purpose. Further, VIASYN reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of VIASYN to notify any person of such revision or changes.

Registered Trademarks: CompuPro, Viasyn Corporation. CP/M-86, Digital Research, Inc.

Compound Trademarks: Concurrent DOS 8-16, CP/M 8-16, Digital Research, Inc. and Viasyn Corporation.

Trademarks: SPUZ, Viasyn Corporation.

All rights reserved. No part of this publication may be reproduced or transmitted in any form, or by any means, without the written permission of VIASYN. Printed and assembled in the United States of America.

# CONTENTS

| ABOUT THE SPUZ                                                            | 1           |

|---------------------------------------------------------------------------|-------------|

| HOW TO GET YOUR SPUZ UP AND RUNNING<br>WITHOUT READING MUCH OF THE MANUAL | 2-3         |

| HARDWARE SECTION.<br>Switches<br>Jumpers                                  | 4-5         |

| THEORY OF OPERATION<br>Overview<br>The Circuitry<br>The DUART             | 8<br>8-13   |

| SOFTWARE SECTION                                                          | 28-29       |

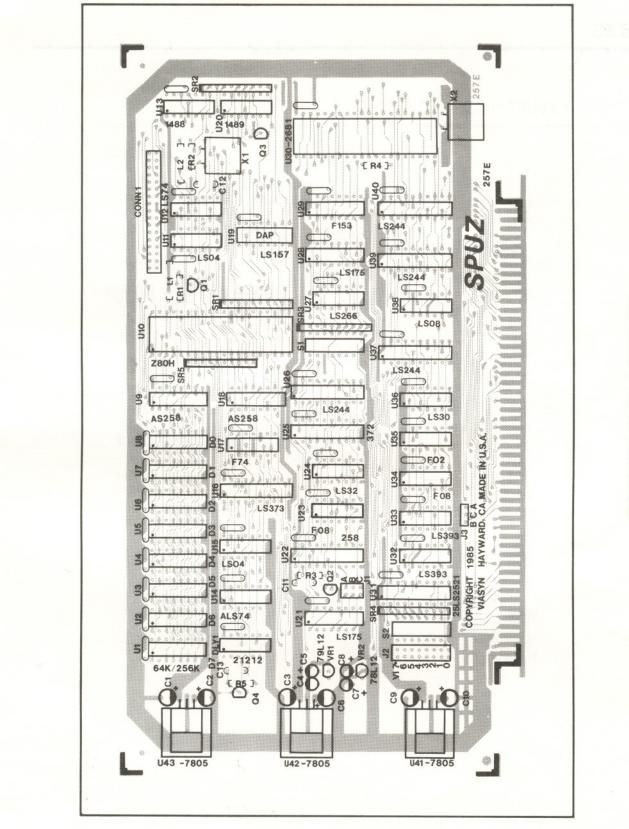

| HARDWARE DESCRIPTION<br>Logic Diagram<br>Parts List<br>Component Layout   | 30-34<br>36 |

oute t.) at

### ABOUT THE SPUZ

VIASYN's SPUZ board combines an 8 MHz Z80H, 64K or 256K of memory and two fully bi-directional RS-232C serial I/O channels to perform a number of "slave processing" tasks.

Because each user has their own processor, memory and serial ports, the overhead on the host system is reduced when the slave is running an 8-bit task. When running 16- or 32-bit programs, the SPUZ can be used as a front end I/O processor adding 8-bit processing capability to your system (as with CompuPro 816/D1, E1, F1, G1 and 286 computers). Up to 16 SPUZs can be resident in the same mainframe.

In systems where high system throughput is necessary, this multiprocessing configuration, in which host and slaves may run 8- and 16-bit software simultaneously, is faster and more efficient than dated dual processing systems where one of the processors is stopped while the other is running.

The SPUZ meets all IEEE 696/S-100 bus specifications and includes the following features:

- Fast 8MHz Z80H for high throughput.

- 64K or 256K bytes of RAM. Up to 16 SPUZ boards occupy only 64K of system memory.

- Dual bi-directional RS-232C serial ports.

- Fully software selectable serial port parameters.

- Supported by CompuPro's Concurrent DOS<sup>™</sup> 8-16<sup>™</sup> multi-user, multi-tasking operating system.

1

- True multi-processing instead of dual processing.

- Ideal as an 8-bit node in a "processor-per-user" system.

- Adds 8-bit capability to 16- or 32-bit systems.

# HOW TO GET YOUR SPUZ UP AND RUNNING WITHOUT READING MUCH OF THE MANUAL

This section is for those of you who are so anxious to see the SPUZ running that you don't want to read the manual. This section will tell you how to set up the SPUZ board so that it can run under Concurrent DOS 8-16 in your system.

### STEP 1. UNPACK THE SPUZ BOARD.

Along with the board, you will find an extra jumper shunt and two card ears in the plastic bag.

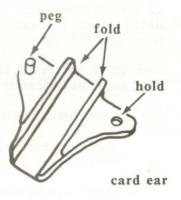

### STEP 2. INSTALL CARD EARS.

- a) Hold the board so the component side is toward you. (See diagram below.)

- b) Insert the peg on the card ear into the hole in the <u>right</u> corner of the board. Fold the ear over the board's edge until the ear's hole snaps over the peg (make sure the long edge of the ear is along the top edge of the board extending toward the center.)

c) Repeat for left ear.

Left Ear

Figure 1. SPUZ (Component Side)

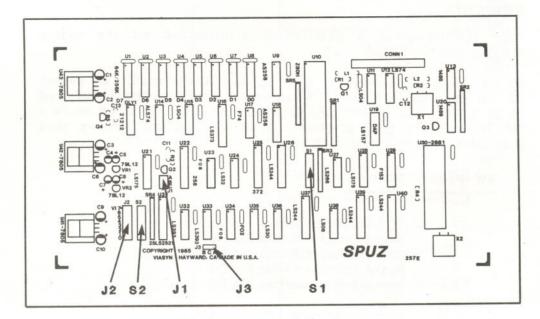

STEP 3. SET SWITCHES. Set the SPUZ switches according to the information in the Hardware Section. (See figure 1 for the location of the switches.)

Figure 2. SPUZ (jumper and switch location)

### **STEP 4. SET JUMPER SHUNT CONNECTIONS**

Install the jumper shunts according to the information in the Hardware Section. See figure 2 for the location of jumper connectors.

### JUMPER SHUNTS

A jumper shunt is a small plastic part used to connect two pins on the jumper connector. Jumper shunts should be installed notch side up.

IF: The board is not correctly jumpered.

THEN: Use a pair of needle nose pliers to gently remove, and carefully replace the jumper shunt in its proper location.

jumper shunt

### INSERT THE SPUZ INTO THE MOTHERBOARD.

Place the board into a slot close to the back of the enclosure. The edge connector is offset, so that the SPUZ will fit <u>only</u> with the component side facing the front panel of the enclosure. **PUSH DOWN** <u>GENTLY</u> UNTIL THE BOARD IS FIRMLY INSTALLED.

### SWITCHES

This section gives a detailed description of all the switch settings for the SPUZ.

In switch S1, positions 4, 5, 6, 7, and 8 are used. In switch S2, all positions are used. Whenever a switch paddle is referred to as a "0", it is in the <u>ON</u> position, and when referred to as a "1", it is in the <u>OFF</u> position. A switch overview follows, then a detailed description of each switch.

SW Paddle Function

| 1 | 4   | Z80 M1 Wait State           |

|---|-----|-----------------------------|

|   | 5   | Board Select Address Bit D3 |

|   | 6   | Board Select Address Bit D2 |

|   | 7   | Board Select Address Bit D1 |

|   | 8   | Board Select Address Bit D0 |

| 2 | 1-8 | Memory Address Bits A23-A16 |

Switch 1 (SW1) - The function of switch 1 positions 5, 6, 7, and 8 is to set the 4-bit Select Address of this board. Up to 16 SPUZ boards can be in a single system, with their memory all addressed at the same 64K page in system memory space, and their 18 I/O ports all overlapping at FC30h-FC41h. Each one must have a different select address. To choose the board that you wish to communicate with, write its select address in the lower nibble to the SLAVESEL port FC40h. You can now communicate with that board's DUART and memory, and the other SPUZ boards are invisible. It is important to always start your communication to a particular SPUZ with a write of the correct select address to the SLAVESEL port FC40h.

SPUZ boards should be numbered starting with 0 and incrementing with each additional board. For a system with one board, the settings should be:

BOARD 0 -- Paddles 5, 6, 7, and 8 ON

For a system with 5 SPUZ boards, the settings should be:

| BOARD 0 | <br>Paddles 5, 6, 7, 8 <u>ON</u>      |

|---------|---------------------------------------|

| BOARD 1 | <br>Paddles 5, 6, 7 ON, paddle 8 OFF  |

| BOARD 2 | <br>Paddles 5, 6, 8 ON, paddle 7 OFF  |

| BOARD 3 | <br>Paddles 5, 6 ON, paddles 7, 8 OFF |

| BOARD 4 | <br>Paddles 5, 7, 8 ON, paddle 6 OFF  |

Finally, SW1 position 4 controls the M1 wait states to the Z80

processor. This switch must be <u>ON</u> when the Z80 is run at 6MHz and above. For 5MHz and below, this switch can be turned off. Since all standard SPUZ boards shipped by VIASYN are 8MHz, leave this switch on. Recommended setting:

### Z80 M1 Wait -- SW1, paddle 4 ON

Switch 2 (SW2) - Switch 2 determines where the 64K page window of SPUZ memory is to appear to the system host and DMA devices. It can appear in any one of 256 pages of memory to CPUs and DMA devices with 24 bits of addressing, and in any one of 16 pages to CPUs and DMA devices with 20 bits of addressing. Paddle 1 is the most significant bit and corresponds with A23, while paddle 8 is the least significant bit and corresponds with A16. For standard CompuPro systems, all SPUZ boards in a mainframe appear in one page. SPUZ boards with 256K of memory also appear as 64K blocks, just the same as a 64K board, and they can be mixed in a system.

The CompuPro standard address is page 0Eh. For the CompuPro standard, all SPUZ boards in a system should be set to:

5

SW2 - MEMORY ADDRESS -- Paddles 1, 2, 3, 4, 8 <u>ON</u>, Paddles 5,6, 7 <u>OFF</u>.

### JUMPERS

This section gives a detailed description of all the jumper settings for the SPUZ.

Jumper J1 is a 6 pin jumper. A shunt can be placed horizontally across A (top), B (middle), C (bottom), or be left as shipped with a closed connection on the solder side across position B. Jumper J2 is a 16 pin jumper. A shunt should be placed horizontally at one of the 8 positions. J2 is shipped with pins installed and a shunt placed across VIO. Jumper J3 is a three pin jumper. A shunt can be placed across A-C (right), B-C (left), or be left as shipped with a closed connection on the solder side across A-C. A jumper overview is next with a detailed explanation of each jumper following.

J Position Function

| 1 | A<br>B<br>C | One S-100 Bus Wait State<br>Two S-100 Bus Wait States (as shipped)<br>Three S-100 Bus Wait States |

|---|-------------|---------------------------------------------------------------------------------------------------|

| 2 | V17<br>V16  | Z80 Interrupt Output to VI7*                                                                      |

|   | VIO<br>VI5  | Z80 Interrupt Output to VI6*<br>Z80 Interrupt Output to VI5*                                      |

|   | VI4         | Z80 Interrupt Output to VI4*                                                                      |

|   | VI3         | Z80 Interrupt Output to VI3*                                                                      |

|   | VI2         | Z80 Interrupt Output to VI2*                                                                      |

|   | VI1         | Z80 Interrupt Output to VI1*                                                                      |

|   | VI0         | Z80 Interrupt Output to VI0*<br>(as shipped)                                                      |

| - |             | E C H-14 O(( (himmed)                                                                             |

3 A-C Four Cycle Hold Off (as shipped) B-C Eight Cycle Hold Off

Jumper J1 - This jumper controls how many wait states the SPUZ inserts into S-100 bus accesses to the memory or I/O ports on the SPUZ. It is a three position jumper. As the total time required to read or write the SPUZ memory is constant, the number of wait states is dependent only on the speed of the host processor. Position A is for one wait state and can be safely used only when the speed of the host processor is 6MHz or less. Position B is for two wait states, and should be used when the processor is 12MHz or less. Position C is for systems faster than 12MHz.

Jumper J1 is shipped with no pins, but with a closed connection on the solder side across position B. This should be left as it is shipped for installation in all CompuPro systems. If special circumstances require this jumper be changed, the trace connecting position B should be cut, pins installed, and a shunt placed in the desired position. Recommended position:

J1 -- Across position B (as shipped).

Jumper J2 - This jumper controls which Vectored Interrupt Line (VI) on the S-100 bus can be asserted by the SPUZ. It is an 8 position jumper, corresponding to 8 VI lines. The Z80 can assert an interrupt to the host by writing a bit pattern to a particular port. The host can clear the interrupt by writing a different bit pattern to a particular port. Any one Vectored Interrupt can be generated.

Jumper J2 is shipped with pins and a shunt across position VIO. VIO is the CompuPro standard for all SPUZ boards. If it is ever desirable to change this, the shunt can be moved to any position. Recommended position:

### J2 -- Across position VIO (as shipped).

Jumper J3 - Jumper J3 controls the bus acknowledge hold off, after access of the Z80's bus. When the host or a DMA device accesses the SPUZ memory or I/O ports, the Z80 is issued a BUSREQ, and sometime later it gives up its internal bus for an external cycle with a BUSACK. If this process took place every time the host or DMA device wanted to access the SPUZ memory, the requestor would waste substantial time in a wait state waiting for the Z80 to issue BUSACK. For this reason, the Z80 is kept in a BUSACK state for a certain time after the last time it was accessed. Thus, when rapid access of the SPUZ memory is occuring (such as when the system is filling SPUZ memory with a program to run), it can happen with a minimum of wait time. Increasing the hold off decreases the host or DMA device wait time when accessing the SPUZ, but reduces the processing throughput of the Z80, and vice-versa.

Our experience and measurements indicate that for most systems, a hold off of 4 bus cycles is a good compromise. If you feel that a larger hold off would be beneficial to your system (for example if your processor was just missing the hold off time in its routine to load programs into the SPUZ memory), the hold off can be increased to 8 bus cycles.

Jumper J3 is normally closed on the solder side of the board across A-C (right side). If it is desirable to increase the hold off to 8 bus cycles, the A-C jumper should be cut, pins installed, and a shunt placed across B-C. Recommended position:

7

J3 -- Across A-C (as shipped).

# THEORY OF OPERATION

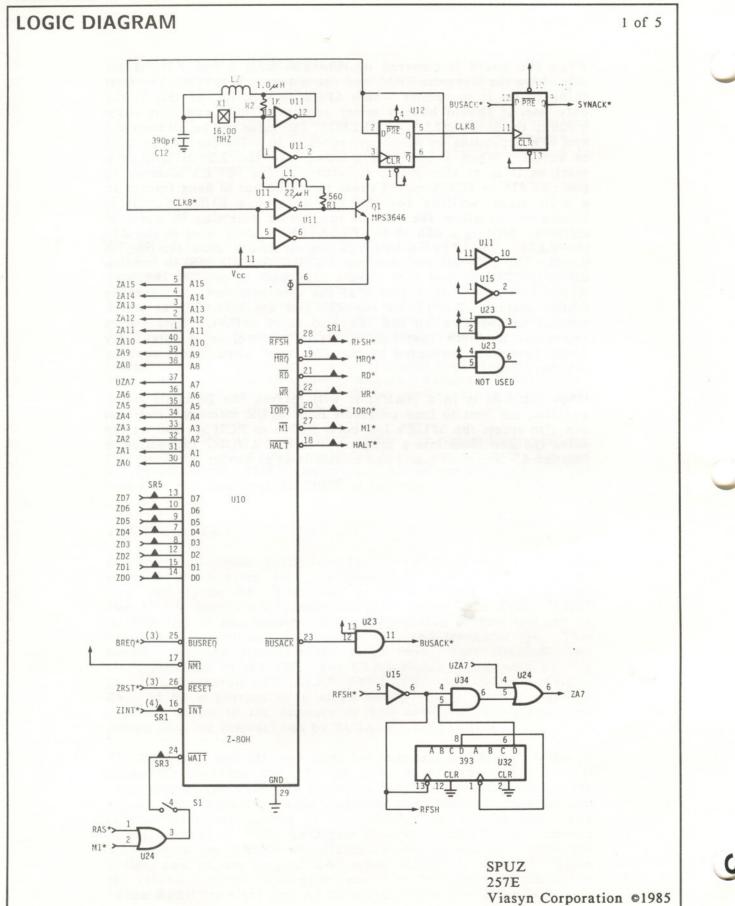

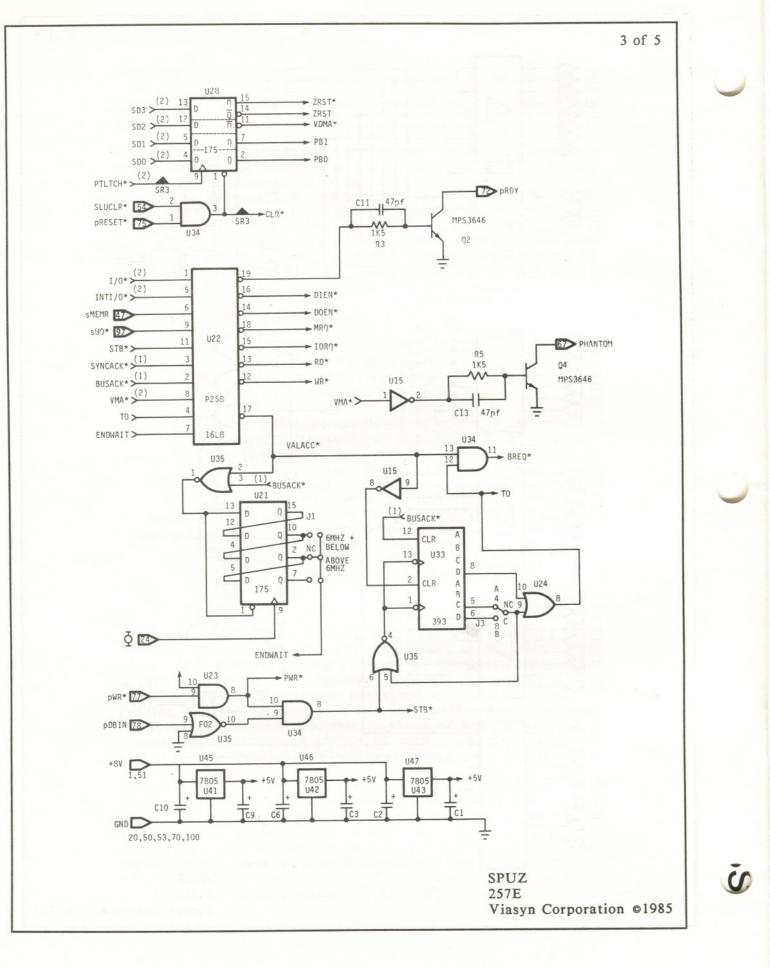

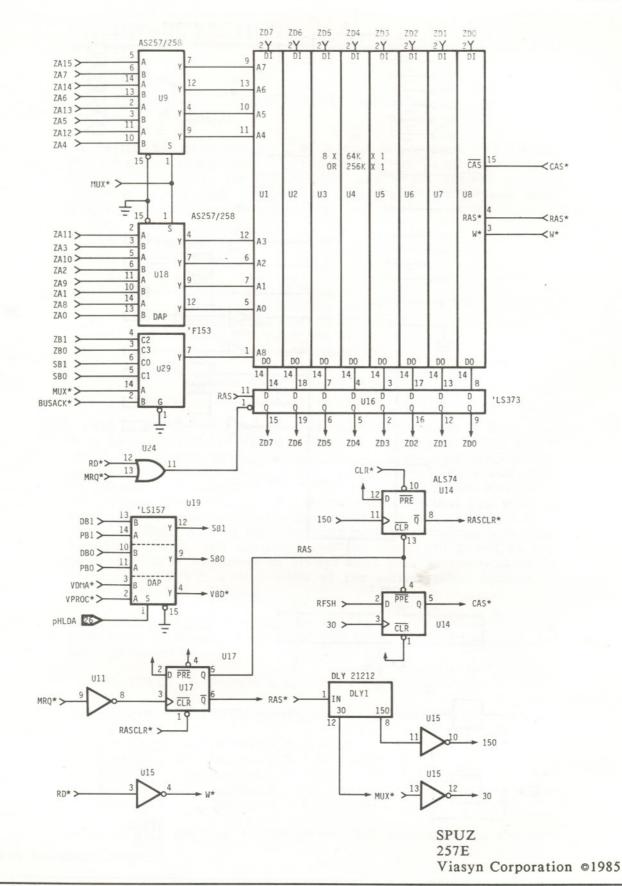

This section of the manual will explain, in general, how the circuitry on the SPUZ works. In the following discussions, it will be helpful to refer to the schematic diagrams contained in the Hardware Description section of this manual.

### **OVERVIEW**

The SPUZ looks like 64K bytes of memory and 18 I/O ports to the S-100 host processor or temporary bus master (DMA device). It does not become a temporary master and is therefore restricted from accessing other user's memory spaces or system peripherals. The S-100 bus has complete access rights to all of the SPUZ's resources including all 64K/256K bytes of memory, both bi-directional serial ports and all internal control ports.

Inter-processor communication is accomplished through a bidirectional interrupt structure. Message passing is through the memory located on the SPUZ. DMA devices can transfer data directly to or from the SPUZ's memory.

There is no EPROM on the SPUZ. When the system is powered up, the on-board Z80 is reset until the S-100 host processor has put a program in the SPUZ's memory and allows the Z80 to run. The host processor can reset the SPUZ at any time.

### THE CIRCUITRY

A 16MHz processor-speed-times-two clock is generated by two sections of inverter U11, inductor L2, resistor R2, capacitor C12, and crystal X1. This clock is fed to the divide by two flip flop U12 to generate a symmetrical 8MHz clock. The signal CLK8\* is then fed to the booster network consisting of two sections of inverter U11, inductor L1, resistor R1, and transistor Q1. This booster network generates the large swing, fast rise/fall time clock required by the Z80. The CLK8 signal is also used by flip flop U12 to generate SYNCACK\*. SYNCACK\* is the BUSACK\* signal delayed by a portion of a clock width. It is used to start an external access to the memory or I/O after the S-100 addresses driven onto the internal bus by BUSACK\* have settled.

The Z80 needs one M1 wait state for processor speeds over 5MHz to guarantee that the DRAM will have data ready. The circuit consisting of OR gate U24 generates WAIT\* to the Z80 during M1 cycles. Most dynamic RAMs (including the 256K parts) require 256 refresh addresses instead of the 128 put out by the Z80. The circuit of inverter U15, AND gate U34, OR gate U24, and counter U32 counts the number of refresh cycles, toggles ZA7 every 128 cycles, and asserts toggled ZA7 when RFSH\* is asserted. Thus, the refresh address is counted from 0 to 256. Non-refresh cycles (when RFSH\* is high) pass A7 from the Z80 to ZA7 directly. The 2681 Dual Asynchronous Receiver/Transmitter (DUART) is I/O mapped into 16 ports of the Z80's I/O space. They are ports 0h to Fh, and are repeated, i.e. port 10h equals port 0h. A description of the ports is contained in the reprint in this manual of the 2681 data sheet.

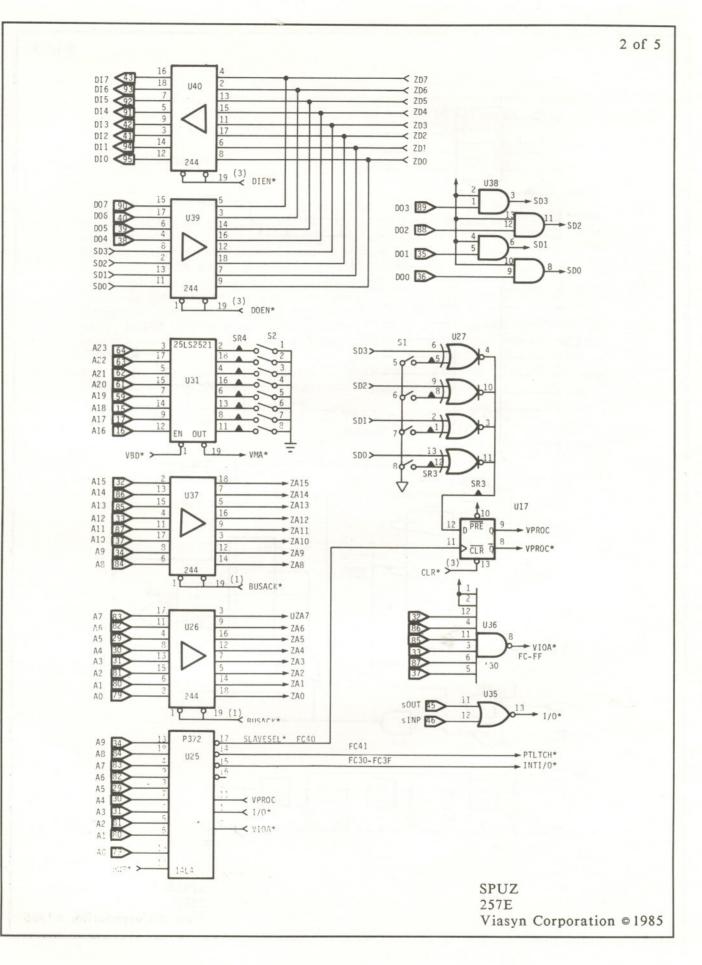

The data bus is buffered by U39 or U40 depending on which direction the transfer is taking place. DIEN\* is asserted on pDBIN when the proper status is met, and DOEN\* is asserted on BUSACK\* when the proper status is met. Part of the DO bus is buffered by U38 to go to the above buffer, the board select comparator (U27), and the parallel port PTLATCH (U28).

The S-100 address bus is buffered onto the internal address bus on BUSACK\* by U26 and U37. PAL U25 (p372) along with AND gate U36, and NOR gate U35 decode the S-100 I/O ports from address FC30h to FC41h. Ports FC40h and FC41h are not mapped on to the internal SPUZ bus, and thus can be written any time regardless of the internal state of the Z80. Ports FC30h to FC3Fh are mapped on to the SPUZ bus, and thus the SPUZ must not be reset when these ports (or SPUZ memory) are accessed or the S-100 bus will hang. The reason for this is that host accesses to the SPUZ internal ports and memory must be arbitrated by the Z80, and if the Z80 is reset when these ports are requested, the Z80 can never issue a BUSACK\* and allow the cycle to take place. Thus, the SPUZ will assert pRDY to wait for the Z80 to give a BUSACK\* (that it will never give if it is reset), and the S-100 system will hang forever in a wait state.

Signal SLAVESEL\* (write port FC40h) will be generated on every SPUZ board in the system when port FC40h is written. Only the one with switch SW1 positions 5, 6, 7, and 8, matching what is on the lower four bits of the DO bus will leave VPROC asserted following a write to the SLAVESEL port. Signal PTLATCH\* (write port FC41h) will be generated only on the board with VPROC asserted when port FC41h is written. Through this port, the host controls ZRST\* to the Z80, VDMA\*, and PB0-PB1, the control for which bank of 64K out of 256K the S-100 bus host accesses. Finally, when VPROC is asserted on either an I/O read or write to ports FC30h to FC3Fh, INTI/O\* is asserted, at which time the DUART is accessed. The S-100 port map is as follows:

| Port                 | Function    |                                                                                                                   |

|----------------------|-------------|-------------------------------------------------------------------------------------------------------------------|

| FC30h<br>to<br>FC3Fh | DUART -     | Maps to ports 0h to Fh of the DUART.<br>For Serial Channels and output bit<br>manipulation. (Read/Write)          |

| FC40h                | SLAVESEL* - | selects which board within a bank of 16 is selected. (Write Only)                                                 |

| FC41h                | PTLATCH* -  | controls RESET, which board is the<br>valid DMA board, and which 64K bank<br>the S-100 bus accesses. (Write Only) |

When the extended address (A16-A23) matches what is set on switch S2 and the signal VBD\* is asserted, comparator U33 asserts VMA\*. The system can access SPUZ internal memory when VMA\* is low, the proper status is met on sMEMR, sWO\* and sOUT, and when pDBIN or pWR\* is asserted. Thus to access a memory location on the SPUZ (when it is running or halted but not reset), first write the proper data pattern to SLAVESEL port FC40h to clock in VPROC on the trailing edge of pWR\*, then access the 64K SPUZ memory window.

The port PTLATCH controls ZRST\*, VDMA\*, PB0, and PB1. Only the host can access this port made from flip flop U28. The bit map of this port is as follows:

| Bit |   | Function (Write Only)                                                          |  |

|-----|---|--------------------------------------------------------------------------------|--|

| D3  | = | ZRST* - Write a one to allow the Z80 to run.<br>Write a zero to reset the Z80. |  |

| D2  | = | VDMA* - Write a one to set DMA board.<br>- Write a zero to turn off DMA board. |  |

|     | = |                                                                                |  |

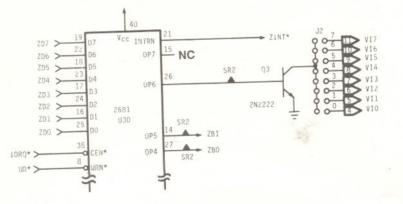

On SPUZ boards with 256K of DRAM, the Z80 can be running out of one of four 64K pages and the S-100 bus can simultaneously access any 64K page. This makes it ideal in multi-user or multi-tasking environments, as the Z80 could be running one program while the host is fetching and loading another program. Furthermore, the host can set up a DMA device to load directly to or from any SPUZ memory page, and simultaneoulsy access any other SPUZ page. Thus, the Z80('s) can be running from one page, the host reading and writing a different page, and a DMA device directly accessing still another page. The pages are controlled by bits PBO and PB1 (Processor Bank 0 and 1), DB0 and DB1 (DMA Bank 0 and 1), and ZB0 and ZB1 (Z80 Bank 0 and 1). When 64K of memory is installed, these bits don't matter. Thus, when the host is accessing the memory, bits PB0 and PB1 from PTLATCH U28 control which 64K page the host sees. When a DMA device is accessing the memory (pHLDA is asserted), DB0 and DB1 from the 2681 OP2 and OP3 control which 64K page the DMA device sees. Finally, when the Z80 is accessing the memory, ZB0 and ZB1 from the 2681 OP4 and OP5 control which 64K page the Z80 sees.

Just as a write to port FC40h (SLAVESEL) selects which SPUZ board of a possible 16 the host (not DMA) will access, setting the VDMA\* signal on one SPUZ selects which board of a possible 16 when a DMA device accesses the SPUZ resources. When a host decides that DMA is to take place to a paticular memory page in a particular SPUZ, the host first selects the particular board via SLAVESEL. Second, the host asserts the VDMA\* signal by writing a 04h (OR'ed with the proper ZRST, PB1, and PB0 bits) to the PTLATCH on the selected board. Third, the host writes to the 2681 on the selected board to choose the proper DB0 and DB1. Now, any DMA to the memory window of the SPUZ(s) will access the properly selected board and the selected page, regardless of further host writes to the SLAVESEL port FC40h.

<u>Warning</u>: Only one SPUZ can have VDMA<sup>\*</sup> asserted at a time. The host MUST turn off the previous VDMA<sup>\*</sup> before asserting a new one. Permanent damage to SPUZ boards may result if more than one board has VDMA<sup>\*</sup> asserted and DMA occurs to the SPUZ window page. Care must also be taken when DMA devices with real time requirements access the SPUZ as it is not guaranteed to give up its internal bus in any specified amount of time. Furthermore, it will lock out the bus for several microseconds every eight consecutive accesses in order to run a refresh cycle.

Once the bits PB0 and PB1, DB0 and DB1, and ZB0 and ZB1 have been selected, multiplexers U29 and U19 control which bits get to the DRAM on what kind of cycle. Depending on the status of BUSACK\* from the Z80 and pHLDA from the S-100, two of these bits will be chosen to produce A8 on RAS and A8 on CAS. If BUSACK\* is not asserted, ZB0 and ZB1 are used. If BUSACK\* is asserted and pHLDA is not, PB0 and PB1 are used. If BUSACK\* and pHLDA are asserted, DB0 and DB1 are used. Multiplexer U19 also selects whether VPROC\* or VDMA\* produces VBD\*. If pHLDA is asserted, VDMA\* is used; if pHLDA is not asserted, VPROC\* is used. This allows the host processor to access a completely different SPUZ than the DMA device is accessing.

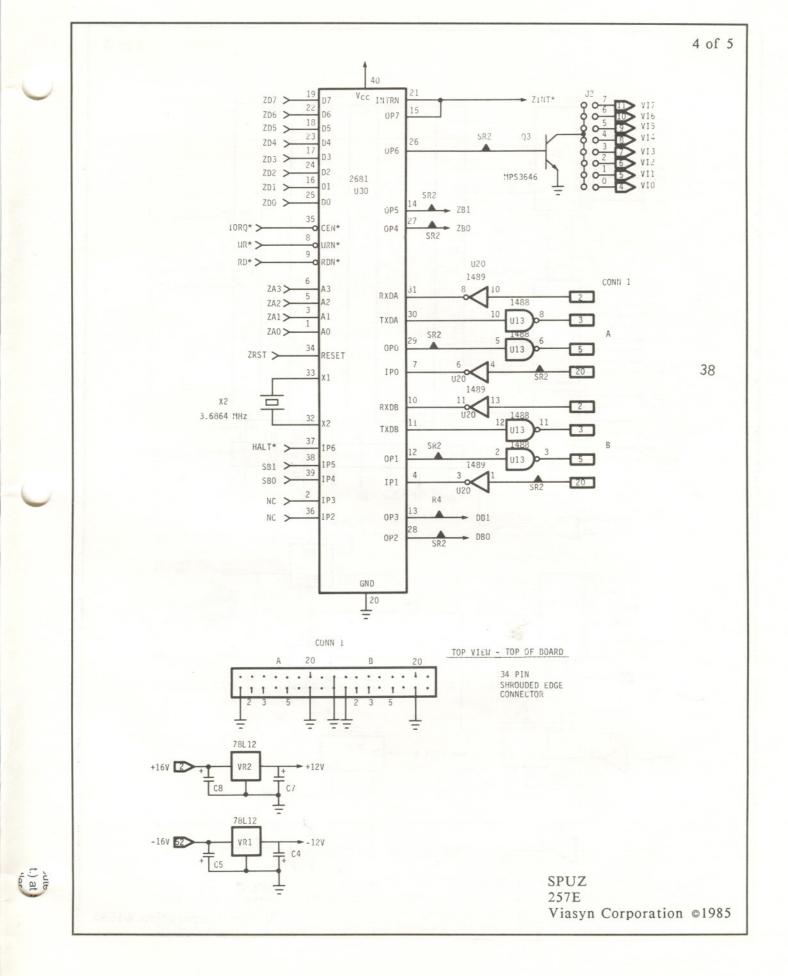

The 2681 DUART handles: 1)the serial receive/transmit function, 2)several output bits necessary on the board, 3)several input bits, and 4)the timer/counter. The 16 ports of the DUART control these functions and are defined in the reprint of the 2681 data sheet included in this manual. The output bits of the 2681 are defined in the following table. All the bits in the OPR are low on reset, and the remarks in parentheses tell what this means to the circuitry.

| Bit        | Function   |                                                                                                                        |

|------------|------------|------------------------------------------------------------------------------------------------------------------------|

| OP7        | ZINT*      | OP7 and INTRN of the 2681 are tied<br>together to Z80 ZINT*. (interrupt<br>not asserted to Z80).                       |

| OP6        | S100<br>VI | S-100 Vectored Interrupt output.<br>(interrupt asserted to S-100 bus).                                                 |

| OP5<br>OP4 | ZB1<br>ZB0 | Controls which 64K bank Z80 sees when 256K parts are installed. (Z80 starts running from bank 3 - high bank).          |

| OP3<br>OP2 | DB1<br>DB0 | Controls which 64K bank DMA sees when 256K parts installed on valid DMA board. (page 3 accessed on reset - high bank). |

| OP1        | RTSB       | Request to Send on B channel of serial<br>port. (inhibits terminal or other<br>device from transmitting to DUART).     |

| OP0        | RTSA       | Request to Send on A channel of serial<br>port. (inhibits terminal or other<br>device from transmitting to DUART).     |

The following table defines the input bits of the 2681.

| Bit        | Function   |                                                                                                  |

|------------|------------|--------------------------------------------------------------------------------------------------|

| IP6        | HALT*      | From HALT* output pin on the Z80. Used to monitor when Z80 is in HALT state.                     |

| IP5<br>IP4 | SB1<br>SB0 | From bits selecting which page the host accesses or last accessed.                               |

| IP3<br>IP2 | OP3<br>OP2 | Not used and not connected.<br>Not used and not connected.                                       |

| IP1        | CTSB       | Clear to Send on channel B. Low when<br>terminal or other device is ready to<br>take characters. |

| IP0        | CTSA       | Clear to Send on channel A. Low when<br>terminal or other device is ready to<br>take characters. |

S-100 bus access to SPUZ resources is controlled by PAL U22 (part p258). It controls the necessary internal status and strobes to run an internal bus cycle. It generates pRDY through capacitor C11 and resistor R5 when the proper status is met, and does not end pRDY until ENDWAIT is generated by counter U21. Thus the chain of events is:

- 1) Host or DMA requests resource (memory or I/O port),

- 2) SPUZ puts host or DMA device in wait state and asserts BREQ\* to the Z80,

- 3) Z80 issues BUSACK\* which starts counter U21, and puts data and address on the internal bus,

- 4) SYNCACK\* is asserted which asserts MRQ\*, IORQ\*, RD\*, or WR\* depending on input status by PAL U22,

- 5) DRAM or DUART cycle is performed, and

- 6) ENDWAIT is asserted which terminates pRDY.

Half of counter U33 controls the hold off which keeps the Z80 in hold by asserting BREQ\* for a certain number of strobes after the last access. The other half of the counter insures that the host does not keep the Z80 in hold too long. If this happened, refresh of the DRAM could be lost. Therefore, the host or DMA device can run no more than 8 cycles on the internal bus before the SPUZ forces the host or DMA device to wait and runs a cycle of its own. In this way, refresh will be maintained. If it is ever necessary to defeat this feature, U24 pin 8 can be removed from the socket, and a small solder bridge can be made from pin 8 to pin 9.

The 2681 interface is straightforward. When the host or the Z80 asserts IORQ\* and either WR\* or RD\*, the 2681 will either accept data or present data to the bus ZD7-ZD0. The address ZA3-ZA0 controls what section of the 2681 is accessed. The port map for the 2681 can be found in the reprint of the 2681 data sheet. The time base for the 2681's baud rate generator and counter/timer is the 3.6864 MHz crystal X2. The 2681 is reset whenever the Z80 is reset as ZRST goes to both chips. Finally, the OP7 bit and INTRN are both able to generate ZINT\* to the Z80, enabling the Z80 to be interrupted by the host, by both serial channels, or by the timer/counter.

The Dynamic RAM circuit provides liberal timing to the RAM chips, while maintaining high speed. The MRQ\* signal's falling edge provides the clock to U17 to start the cycle. The delay line DLY1 then controls the timing, asynchronously from the 8MHz clock. When the data is ready on a read cycle, it is latched in U16 to be read by the Z80 or host. On a write, data flows off the ZD0-ZD7 lines into the DRAM when W\* is asserted.

Either eight 64K parts or eight 256K parts can be used in the SPUZ. The 64K board has multiplexer U29 missing. If you decide to upgrade your 64K board to 256K, a factory upgrade can be obtained from VIASYN. We will install the 256K parts, multiplexer U29, and run a complete confidence test.

t.) at

### THE DUART

Part of Signetics' data sheet for the SC2681 Dual Asynchronous Receiver/Transmitter (DUART) is reprinted here with permission. The complete data sheet can be found in the Signetics MOS Microprocessor Data Manual for 1982 or later, and can be obtained by writing or calling Signetics, 811 East Arques Avenue, P.O. Box 409, Sunnyvale, California 94086, (408)739-7700.

### Preliminary

### DESCRIPTION

The Signetics SCN2681 Dual Universal Asynchronous Receiver/Transmitter (DUART) is a single chip MOS-LSI communications device that provides two independent full-duplex asynchronous receiver/transmitter channels in a single package. It interfaces directly with microprocessors and may be used in a polled or interrupt driven system.

The operating mode and data format of each channel can be programmed independently. Additionally, each receiver and transmitter can select its operating speed as one of eighteen fixed baud rates, a 16x clock derived from a programmable counter/timer, or an external 1x or 16x clock. The baud rate generator and counter/timer can operate directly from a crystal or from external clock inputs. The ability to independently program the operating speed of the receiver and transmitter make the DUART particularly attractive for dual-speed channel applications such as clustered terminal systems.

Each receiver is quadruply buffered to minimize the potential of receiver overrun or to reduce interrupt overhead in interrupt driven systems. In addition, a flow control capability is provided to disable a remote DUART transmitter when the buffer of the receiving device is full.

Also provided on the SCN2681 are a multipurpose 7-bit input port and a multipurpose 8-bit output port. These can be used as general purpose I/O ports or can be assigned specific functions (such as clock inputs or status/interrupt outputs) under program control.

The SCN2681 is available in three package versions to satisfy various system requirements: 40-pin and 28-pin, both 0.6" wide DIPs, and a compact 24-pin, 0.4" wide, DIP.

### **FEATURES**

- Dual full-duplex asynchronous receiver/ transmiter

- Quadruple buffered receiver data registers

- Programmable data format

5 to 8 data bits plus parity

- -5 to 8 data bits plus parity

- Odd, even, no parity or force parity

-1, 1.5 or 2 stop bits programmable in 1/16 bit increments

- Programmable baud rate for each receiver and transmiter selectable from: —18 fixed rates: 50 to 38.4K baud

- -One user defined rate derived from programmable timer/counter

- -External 1x or 16x clock

- Parity, framing, and overrun error detection

- · False start bit detection

- · Line break detection and generation

- · Programmable channel mode

- -Normal (full duplex)

- -Automatic echo

- -Local loopback

- -Remote loopback

- Multi-function programmable 16-bit counter/timer

- Multi-function 7-bit input port

- Can serve as clock or control inputs

Change of state detection on four inputs

- Multi-function 8-bit output port

- -Individual bit set/reset capability

- -Outputs can be programmed to be status/interrupt signals

- · Versatile interrupt system

- -Single interrupt output with eight maskable interrupting conditions

- Output port can be configured to provide a total of up to six separate wire-OR'able interrupt outputs

- Maximum data transfer: 1X 1MB/sec, 16X — 125KB/sec

- Automatic wake-up mode for multidrop applications

- Start-end break interrupt/status

- Detects break which originates in the middle of a character

- On-chip crystal oscillator

- TTL compatible

- Single + 5V power supply

### ORDERING CODE

|  | PACKAGES                   | $V_{CC} = 5V \pm 5\%$ , $T_A = 0^{\circ}C$ to 70°C |                                |                                |

|--|----------------------------|----------------------------------------------------|--------------------------------|--------------------------------|

|  | FACKAGES                   | 24 Pin <sup>1</sup>                                | 28 Pin <sup>2</sup>            | 40 Pin <sup>2</sup>            |

|  | Ceramic DIP<br>Plastic DIP | Not available<br>SCN2681AC1N24                     | SCN2681AC1128<br>SCN2681AC1N28 | SCN2681AC1I40<br>SCN2681AC1N40 |

<sup>1</sup>400 mil wide DIP <sup>2</sup>600 mil wide DIP

### **PIN CONFIGURATION**

| A0 1                                        | 40 VCC                              |

|---------------------------------------------|-------------------------------------|

| IP3 2                                       | 40 ♥CC<br>39 IP4                    |

| A1 3                                        | 38 IP5                              |

| IP1 4                                       | 37 IP6                              |

|                                             |                                     |

| A2 5                                        | 36 IP2                              |

| A3 6                                        | 35 CEN                              |

|                                             | 34 RESET                            |

|                                             | 33 X2                               |

| RDN 9                                       | 32 X1/CLK                           |

| RXDB 10                                     | 31 RXDA                             |

| TXDB 11                                     | 30 TXDA                             |

| OP1 12                                      | 29 OP0                              |

| OP3 13                                      | 28 OP2                              |

| OP5 14                                      | 27 OP4                              |

| OP7 15                                      | 26 OP6                              |

| D1 16                                       | 25 D0                               |

| D3 17                                       | 24 D2                               |

| D5 18                                       | 23 D4                               |

| D7 19                                       | 22 D6                               |

| GND 20                                      | 21 INTRN                            |

|                                             |                                     |

| A0 1                                        |                                     |

| _                                           | 28 VCC                              |

| A1 2                                        | 27 IP2                              |

| A2 3                                        | 26 CEN                              |

| A3 4                                        | 25 RESET                            |

| WRN 5                                       | 24 X2                               |

| RDN 6                                       | 23 X1/CLK                           |

|                                             |                                     |

| RXDB 7                                      | 22 RXDA                             |

|                                             | 21 TXDA                             |

| RXDB 7                                      |                                     |

| RXDB 7<br>TXDB 8                            | 21 TXDA                             |

| RXDB 7<br>TXDB 8<br>OP1 9                   | 21 TXDA<br>20 OP0                   |

| RXDB 7<br>TXDB 8<br>OP1 9<br>D1 10          | 21 TXDA<br>20 OP0<br>19 D0          |

| RXDB 7<br>TXDB 8<br>OP1 9<br>D1 10<br>D3 11 | 21 TXDA<br>20 OP0<br>19 D0<br>18 D2 |

| A1 1   | 24 A0     |

|--------|-----------|

| A2 2   | 23 VCC    |

| A3 3   | 22 CEN    |

| WRN 4  | 21 RESET  |

| RDN 5  | 20 X1/CLK |

| RXDB 6 | 19 RXDA   |

| TXDB 7 | 18 TXDA   |

| D1 8   | 17 D0     |

| D3 9   | 16 D2     |

| D5 10  | 15 D4     |

| D7 11  | 14 D6     |

| GND 12 | 13 INTRN  |

|        |           |

| TOP V  | IEWS      |

### Preliminary

### **BLOCK DIAGRAM**

1

## Preliminary

t.) at tler

### PIN DESIGNATION

| MNEMONIC | APPLICABLE |    | TYPE | NAME AND EUNOTION |                                                                                                                                                                                                                                                               |

|----------|------------|----|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 40         | 28 | 24   | ITPE              | NAME AND FUNCTION                                                                                                                                                                                                                                             |

| D0-D7    | X          | х  | X    | I/O               | Data Bus: Bidirectional 3-state data bus used to transfer commands, data and status betwee<br>the DUART and the CPU. D0 is the least significant bit.                                                                                                         |

| CEN      | x          | х  | ×    | I                 | <b>Chip Enable:</b> Active low input signal. When low, data transfers between the CPU and the DUART are enabled on D0-D7 as controlled by the WRN, RDN and A0-A3 inputs. When hig places the D0-D7 lines in the 3-state condition.                            |

| WRN      | x          | x  | x    | 1                 | Write Strobe: When low and CEN is also low, the contents of the data bus is loaded into the addressed register. The transfer occurs on the rising edge of the signal.                                                                                         |

| RDN      | x          | х  | x    | 1                 | <b>Read Strobe:</b> When low and CEN is also low, causes the contents of the addressed register be presented on the data bus. The read cycle begins on the falling edge of RDN.                                                                               |

| A0-A3    | X          | х  | X    | 1                 | Address Inputs: Select the DUART internal registers and ports for read/write operations.                                                                                                                                                                      |

| RESET '  | X          | X  | x    | 1                 | <b>Reset:</b> A high level clears internal registers (SRA, SRB, IMR, ISR, OPR, OPCR), puts OP0-OF in the high state, stops the counter/timer, and puts channels A and B in the inactive stat with the TxDA and TxDB outputs in the mark (high) state.         |

| INTRN    | X          | Х  | x    | 0                 | Interrupt Request: Active low, open drain, output which signals the CPU that one or more the eight maskable interrupting conditions are true.                                                                                                                 |

| X1/CLK   | X          | х  | X    | 1                 | <b>Crystal 1:</b> Crystal or external clock input. A crystal or clock of the specified limits must be supplied at all times. When a crystal is used, a capacitor must be connected from this pint ground (see figure 5).                                      |

| X2       | x          | х  |      | 0                 | <b>Crystal 2:</b> Connection for other side of the crystal. Should be connected to ground if crystal is not used. When a crystal is used, a capacitor must be connected from this pin ground (see figure 5).                                                  |

| RxDA     | X          | Х  | x    | 1                 | Channel A Receiver Serial Data Input: The least significant bit is received first. 'Mark' is hig<br>'space' is low.                                                                                                                                           |

| RxDB     | X          | Х  | x    | 1                 | Channel B Receiver Serial Data Input: The least significant bit is received first. 'Mark' is hig<br>'space' is low.                                                                                                                                           |

| TxDA     | X          | X  | x    | 0                 | <b>Channel A Transmitter Serial Data Output:</b> The least significant bit is transmitted first. The output is held in the 'mark' condition when the transmitter is disabled, idle, or when operating in local loopback mode. 'Mark' is high, 'space' is low. |

| TxDB     | X          | Х  | X    | 0                 | <b>Channel B Transmitter Serial Data Output:</b> The least significant bit is transmitted first. The output is held in the 'mark' condition when the transmitter is disabled, idle, or when operating in local loopback mode. 'Mark' is high, 'space' is low. |

| OP0      | X          | Х  |      | 0                 | Output 0: General purpose output, or channel A request to send (RTSAN, active low). Can I deactivated on receive or transmit.                                                                                                                                 |

| OP1      | х          | х  |      | 0                 | Output 1: General purpose output, or channel B request to send (RTSBN, active low). Can deactivated on receive or transmit.                                                                                                                                   |

| OP2      | х          |    |      | 0                 | Output 2: General purpose output, or channel A transmitter 1X or 16X clock output, or channel A receiver 1X clock output.                                                                                                                                     |

| OP3      | х          |    |      | 0                 | Output 3: General purpose output, or open drain, active low counter/timer output, or channel B transmitter 1X clock output, or channel B receiver 1X clock output.                                                                                            |

| OP4      | x          |    | •    | 0                 | Output 4: General purpose output, or channel A open drain, active low, RxRDYA/FFULLA ou<br>put.                                                                                                                                                               |

| OP5      | X          |    |      | 0                 | Output 5: General purpose output, or channel B open drain, active low, RxRDYB/FFULLB ou put.                                                                                                                                                                  |

| OP6      | х          |    |      | 0                 | Output 6: General purpose output, or channel A open drain, active low, TxRDYA output.                                                                                                                                                                         |

| OP7      | х          |    |      | 0                 | Output 7: General purpose output, or channel B open drain, active low, TxRDYB output.                                                                                                                                                                         |

| IPO      | х          |    |      | 1                 | Input 0: General purpose input, or channel A clear to send active low input (CTSAN).                                                                                                                                                                          |

| IP1      | х          |    |      | 1                 | Input 1: General purpose input, or channel B clear to send active low input (CTSBN).                                                                                                                                                                          |

| IP2      | х          | Х  | -    | 1                 | Input 2: General purpose input, or counter/timer external clock input.                                                                                                                                                                                        |

| IP3      | x          |    |      | I                 | <b>Input 3</b> : General purpose input, or channel A transmitter external clock input (TxCA). When<br>the external clock is used by the transmitter, the transmitted data is clocked on the fallin<br>edge of the clock.                                      |

17

### Preliminary

PIN DESIGNATION (Continued)

|                 | APPLICABLE |    | TYPE | NAME AND FUNCTION |                                                                                                                                                                                                                    |  |  |  |  |

|-----------------|------------|----|------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MNEMONIC        | 40         | 28 | 24   | TTPE              | NAME AND FUNCTION                                                                                                                                                                                                  |  |  |  |  |

| IP4             | X          |    |      | 1                 | Input 4: General purpose input, or channel A receiver external clock input (RxCA). When the external clock is used by the receiver, the received data is sampled on the rising edge of the clock.                  |  |  |  |  |

| IP5             | X          |    |      | I                 | <b>Input 5:</b> General purpose input, or channel B transmitter external clock input (TxCB). When the external clock is used by the transmitter, the transmitted data is clocked on the falling edge of the clock. |  |  |  |  |

| IP6             | X          |    |      | 1                 | <b>Input 6:</b> General purpose input or channel B receiver external clock input (RxCB). When the external clock is used by the receiver, the received data is sampled on the rising edge of the clock.            |  |  |  |  |

| V <sub>cc</sub> | х          | x  | ×    | 1                 | Power Supply: + 5V supply input                                                                                                                                                                                    |  |  |  |  |

| GND             | x          | X  | X    | 1                 | Ground                                                                                                                                                                                                             |  |  |  |  |

### **BLOCK DIAGRAM**

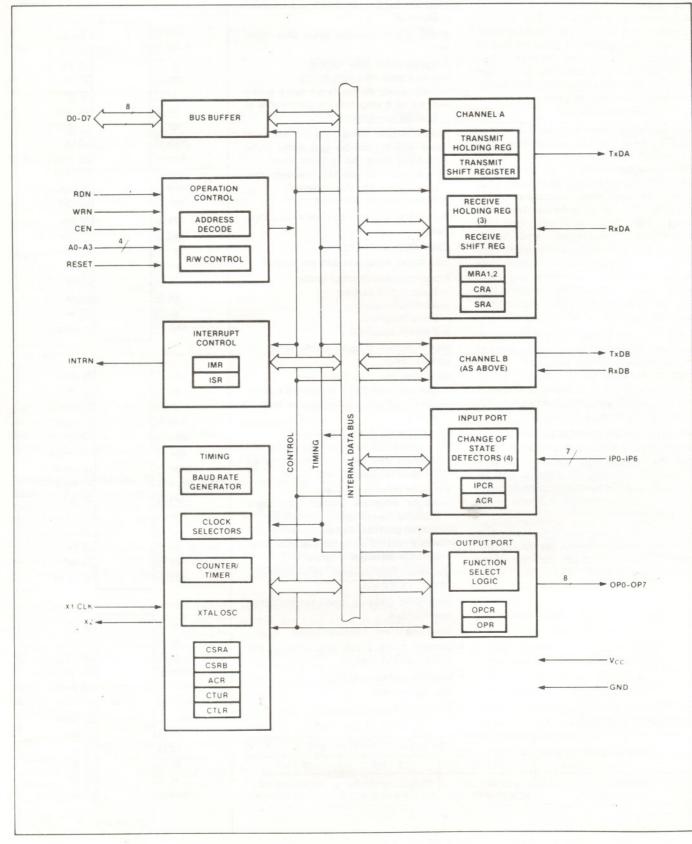

The 2681 DUART consists of the following eight major sections: data bus buffer, operation control, interrupt control, timing, communications channels A and B, input port and output port. Refer to the block diagram.

### **Data Bus Buffer**

The data bus buffer provides the interface between the external and internal data busses. It is controlled by the operation control block to allow read and write operations to take place between the controlling CPU and the DUART.

### **Operation Control**

The operation control logic receives operation commands from the CPU and generates appropriate signals to internal sections to control device operation. It contains address decoding and read and write circuits to permit communications with the microprocessor via the data bus buffer.

### Interrupt Control

A single active low interrupt output (INTRN) is provided which is activated upon the occurence of any of eight internal events. Associated with the interrupt system are the interrupt mask register (IMR) and the interrupt status register (ISR). The IMR may be programmed to select only certain conditions to cause INTRN to be asserted. The ISR can be read by the CPU to determine all currently active interrupting conditions.

Outputs OP3-OP7 can be programmed to provide discrete interrupt outputs for the transmitters, receivers, and counter/timer.

### **Timing Circuits**

The timing block consists of a crystal oscillator, a baud rate generator, a programmable 16-bit counter/timer, and four clock selectors. The crystal oscillator operates directly from a 3.6864MHz crystal connected across the X1/CLK and X2 inputs. If an external clock of the appropriate frequency is available, it may be connected to X1/CLK. The clock serves as the basic timing reference for the baud rate generator (BRG), the counter/timer, and other internal circuits. A clock signal within the limits specified in the specifications section of this data sheet must always be supplied to the DUART.

The baud rate generator operates from the oscillator or external clock input and is capable of generating 18 commonly used data communications baud rates ranging from 50 to 38.4K baud. The clock outputs from the BRG are at 16X the actual baud rate. The counter/timer can be used as a timer to produce a 16X clock for any other baud rate by counting down the crystal clock or an external clock. The four clock selectors allow the independent selection, for each receiver and transmitter, of any of these baud rates or an external timing signal.

The counter/timer (C/T) can be programmed to use one of several timing sources as its input. The output of the C/T is available to the clock selectors and can also be programmed to be output at OP3. In the counter mode, the contents of the C/T can be read by the CPU and it can be stopped and started under program control. In the timer mode, the C/T acts as a programmable divider.

### Communications Channels A and B

Each communications channel of the 2681 comprises a full duplex asynchronous receiver/transmitter (UART). The operating frequency for each receiver and transmitter can be selected independently from the baud rate generator, the counter timer, or from an external input.

The transmitter accepts parallel data from the CPU, converts it to a serial bit stream, inserts the appropriate start, stop, and optional parity bits and outputs a composite serial stream of data on the TxD output pin. The receiver accepts serial data on the RxD pin, converts this serial input to parallel format, checks for start bit, stop bit, parity bit (if any), or break condition and sends an assembled character to the CPU.

### Input Port

The inputs to this unlatched 7-bit port can be read by the CPU by performing a read operation at address  $D_{16}$ . A high input results in a logic 1 while a low input results in a logic 0.  $D_7$  will always be read as a logic 1. The pins of this port can also serve as auxiliary inputs to certain portions of the DUART logic.

Four change-of-state detectors are provided which are associated with inputs IP3, IP2, IP1, and IP0. A high-to-low or lowto-high transition of these inputs lasting longer than 25-50µs will set the corresponding bit in the input port will change register. The bits are cleared when the register is read by the CPU. Any change of state can also be programmed to generate an interrupt to the CPU.

### Preliminary

### **Output Port**

The 8-bit multi-purpose output port can be used as a general purpose output port, in which case the outputs are the complements of the output port register (OPR). OPR[n] = 1 results in OP[n] = low and viceversa. Bits of the OPR can be individually set and reset. A bit is set by performing a write operation at address  $E_{16}$  with the accompanying data specifying the bits to be set (1 = set, 0 = no change). Likewise, a bit is reset by a write at address  $F_{16}$  with the accompanying data specifying the bits to be reset (1 = reset, 0 = no change).

Outputs can be also individually assigned specific functions by appropriate programming of the channel A mode registers (MR1A, MR2A), the channel B mode registers (MR1B, MR2B), and the output port configuration register (OPCR).

### **OPERATION**

### Transmitter

The 2681 is conditioned to transmit data when the transmitter is enabled through the command register. The 2681 indicates to the CPU that it is ready to accept a character by setting the TxRDY bit in the status register. This condition can be programmed to generate an interrupt request at OP6 or OP7 and INTRN. When a character is loaded into the transmit holding register (THR), the above conditions are negated. Data is transferred from the holding register to the transmit shift register when it is idle or has completed transmission of the previous character. The TxRDY conditions are then asserted again which means one full character time of buffering is provided. Characters cannot be loaded into the THR while the transmitter is disabled

The transmitter converts the parallel data from the CPU to a serial bit stream on the TxD output pin. It automatically sends a start bit followed by the programmed number of data bits, an optional parity bit, and the programmed number of stop bits. The least significant bit is sent first. Following the transmission of the stop bits, if a new character is not available in the THR, the TxD output remains high and the TxEMT bit in the status register (SR) will be set to 1. Transmission resumes and the TxEMT bit is cleared when the CPU loads a new character into the THR. If the transmitter is disabled, it continues operating until the character currently being transmitted is completely sent out. The transmitter can be forced to send a continuous low condition by issuing a send break command.

The transmitter can be reset through a software command. If it is reset, operation ceases immediately and the transmitter must be enabled through the command register before resuming operation. If CTS operation is enabled, the CTSN input must be low in order for the character to be transmitted, if it goes high in the middle of a transmission, the character in the shift register is transmitted and TxDA then remains in the marking state until CTSN goes low. The transmitter can also control the deactivation of the RTSN output. If programmed, the RTSN output will be reset one bit time after the character in the transmit shift register and transmit holding register (if any) are completely transmitted, if the transmitter has been disabled

### Receiver

The 2681 is conditioned to receive data when enabled through the command register. The receiver looks for a high to low (mark to space) transition of the start bit on the RxD input pin. If a transition is detected, the state of the RxD pin is sampled each 16X clock for 7-1/2 clocks (16X clock mode) or at the next rising edge of the bit time clock (1X clock mode). If RxD is sampled high, the start bit is invalid and the search for a valid start bit begins again. If RxD is still low, a valid start bit is assumed and the receiver continues to sample the input at one bit time intervals at the theoretical center of the bit, until the proper number of data bits and the parity bit (if any) have been assembled, and one stop bit has been detected. The least sigificant bit is received first. The data is then transferred to the receive holding register (RHR) and the RxRDY bit in the SR is set to a 1. This condition can be programmed to generate an interrupt at OP4 or OP5 and INTRN. If the character length is less than eight bits, the most significant unused bits in the RHR are set to zero.

After the stop bit is detected, the receiver will immediately look for the next start bit. However, if a non-zero character was received without a stop bit (framing error) and RxD remains low for one half of the bit period after the stop bit was sampled, then the receiver operates as if a new start bit transition had been detected at that point (one-half bit time after the stop bit was sampled).

The parity error, framing error, overrun error and received break state (if any) are strobed into the SR at the received character boundary, before the RxRDY status bit is set. If a break condition is detected (RxD is low for the entire character including the stop bit), a character consisting of all zeros will be loaded into the RHR and the received break bit in the SR is set to 1. The RxD input must return to a high condition for at least one-half bit time before a search for the next start bit begins.

The RHR consists of a first-in-first-out (FIFO) stack with a capacity of three characters. Data is loaded from the receive shift register into the topmost empty position of the FIFO. The RxRDY bit in the status register is set whenever one or more characters are available to be read, and a FFULL status bit is set if all three stack positions are filled with data. Either of these bits can be selected to cause an interrupt. A read of the RHR outputs the data at the top of the FIFO. After the read cycle, the data FIFO and its associated status bits (see below) are 'popped' thus emptying a FIFO position for new data.

In addition to the data word, three status bits (parity error, framing error, and received break) are also appended to each data character in the FIFO (overrun is not). Status can be provided in two ways, as programmed by the error mode control bit in the mode register. In the 'character' mode, status is provided on a characterby-character basis: the status applies only to the character at the top of the FIFO. In the 'block' mode, the status provided in the SR for these three bits is the logical OR of the status for all characters coming to the top of the FIFO since the last 'reset error' command was issued. In either mode reading the SR does not affect the FIFO. The FIFO is 'popped' only when the RHR is read. Therefore the status register should be read prior to reading the FIFO.

If the FIFO is full when a new character is received, that character is held in the receive shift register until a FIFO position is available. If an additional character is received while this state exits, the contents of the FIFO are not affected: the character previously in the shift register is lost and the overrun error status bit (SR[4]) will be set upon receipt of the start bit of the new (overruning) character.

The receiver can control the deactivation of RTS. If programmed to operate in this mode, the RTSN output will be negated when a valid start bit was received and the FIFO is full. When a FIFO position becomes available, the RTSN output will be re-asserted automatically. This feature can be used to prevent an overrun, in the

### Preliminary

receiver, by connecting the RTSN output to the CTSN input of the transmitting device.

If the receiver is disabled, the FIFO characters can be read. However, no additional characters can be received until the receiver is enabled again. If the receiver is reset, the FIFO and all of the receiver status, and the corresponding output ports and interrupt are reset. No additional characters can be received until the receiver is enabled again.

### **Multidrop Mode**

The DUART is equipped with a wake up mode used for multidrop applications. This mode is selected by programming bits MR1A[4:3] or MR1B[4:3] to '11' for channels A and B respectively. In this mode of operation, a 'master' station transmits an address character followed by data characters for the addressed 'slave' station. The slave stations, with receivers that are normally disabled, examine the received data stream and 'wakeup' the CPU (by setting RxRDY) only upon receipt of an address character. The CPU compares the received address to its station address and enables the receiver if it wishes to receive the subsequent data characters. Upon receipt of another address character, the CPU may disable the receiver to initiate the process again.

A transmitted character consists of a start bit, the programmed number of data bits, an address/data (A/D) bit, and the programmed number of stop bits. The polarity of the transmitted A/D bit is selected by the CPU by programming bit MR1A[2]/ MR1B[2]. MR1A[2]/MR1B[2] = 0 transmits a zero in the A/D bit position, which identifies the corresponding data bits as data, while MR1A[2]/MR1B[2] = 1 transmits a one in the A/D bit position, which identifies the corresponding data bits as an address. The CPU should program the mode register prior to loading the corresponding data bits into the THR.

In this mode, the receiver continuously looks at the received data stream, whether it is enabled or disabled. If disabled, it sets the RxRDY status bit and loads the character into the RHR FIFO if the received A/D bit is a one (address tag), but discards the received character if the received A/D bit is a zero (data tag). If enabled, all received characters are transferred to the CPU via the RHR. In either case, the data bits are loaded into the data FIFO while the A/D bit is loaded into the status FIFO position normally used for parity error (SRA[5] or SRB[5]). Framing error, overrun error, and break detect operate normally whether or not the receiver is enabled.

### PROGRAMMING

The operation of the DUART is programmed by writing control words into the appropriate registers. Operational feedback is provided via status registers which can be read by the CPU. The addressing of the registers is described in table 1.

The contents of certain control registers are initialized to zero on RESET. Care should be exercised if the contents of a register are changed during operation, since certain changes may cause operational problems. For example, changing the number of bits per character while the transmitter is active may cause the transmission of an incorrect character. In general, the contents of the MR, the CSR, and the OPCR should only be changed while the receiver(s) and transmitter(s) are not enabled, and certain changes to the ACR should only be made while the C/T is stopped.

Mode registers 1 and 2 of each channel are accessed via independent auxiliary pointers. The pointer is set to MR1x by RESET or by issuing a 'reset pointer' command via the corresponding command register. Any read or write of the mode register while the pointer is at MR1x switches the pointer to MR2x. The pointer then remains at MR2x, so that subsequent accesses are always to MR2x unless the pointer is reset to MR1x as described above.

Mode, command, clock select, and status registers are duplicated for each channel to provide total independent operation and control. Refer to table 2 for register bit descriptions.

### MR1A — Channel A Mode Register 1

MR1A is accessed when the channel A MR pointer points to MR1. The pointer is set to MR1 by RESET or by a 'set pointer' command applied via CRA. After reading or writing MR1A, the pointer will point to MR2A.

MR1A[7] — Channel A Receiver Requestto-Send Control — This bit controls the deactivation of the RTSAN output (OP0) by the receiver. This output is normally asserted by setting OPR[0] and negated by resetting OPR[0]. MR1A[7] = 1 causes RTSAN to be negated upon receipt of a valid start bit if the channel A FIFO is full. However, OPR[0] is not reset and RTSAN will be asserted again when an empty FIFO position is available. This feature can be used for flow control to prevent overrun in the receiver by using the RTSAN output signal to control the CTSN input of the transmitting device.

MR1A[6] — Channel A Receiver Interrupt Select — This bit selects either the channel A receiver ready status (RXRDY) or the channel A FIFO full status (FFULL) to be used for CPU interrupts. It also causes the selected bit to be output on OP4 if it is programmed as an interrupt output via the OPCR.

MR1A[5] — Channel A Error Mode Select — This bit selects the operating mode of the three FIFOed status bits (FE, PE, received break) for channel A. In the 'character' mode, status is provided on a character-by-character basis: the status applies only to the character at the top of the FIFO. In the 'block' mode, the status provided in the SR for these bits is the ac-

### Table 1 2681 REGISTER ADDRESSING

| A3 | A2 | A1 | AO | READ (RDN = 0)                | WRITE (WRN = 0)                |

|----|----|----|----|-------------------------------|--------------------------------|

| 0  | 0  | 0  | 0  | Mode Register A (MR1A, MR2A)  | Mode Register A (MR1A, MR2A)   |

| 0  | 0  | 0  | 1  | Status Register A (SRA)       | Clock Select Reg. A (CSRA)     |

| 0  | 0  | 1  | 0  | *Reserved*                    | Command Register A (CRA)       |

| 0  | 0  | 1  | 1  | RX Holding Register A (RHRA)  | TX Holding Register A (THRA)   |

| 0  | 1  | 0  | 0  | Input Port Change Reg. (IPCR) | Aux. Control Register (ACR)    |

| 0  | 1  | 0  | 1  | Interrupt Status Reg. (ISR)   | Interrupt Mask Reg. (IMR)      |

| 0  | 1  | 1  | 0  | Counter/Timer Upper (CTU)     | C/T Upper Register (CTUR)      |

| 0  | 1  | 1  | 1  | Counter/Timer Lower (CTL)     | C/T Lower Register (CTLR)      |

| 1  | 0  | 0  | 0  | Mode Register B (MR1B, MR2B)  | Mode Register B (MR1B, MR2B)   |

| 1  | 0  | 0  | 1  | Status Register B (SRB)       | Clock Select Reg. B (CSRB)     |

| 1  | 0  | 1  | 0  | *Reserved*                    | Command Register B (CRB)       |

| 1  | 0  | 1  | 1  | RX Holding Register B (RHRB)  | TX Holding Register B (THRB)   |

| 1  | 1  | 0  | 0  | *Reserved*                    | *Reserved*                     |

| 1  | 1  | 0  | 1  | Input Port                    | Output Port Conf. Reg. (OPCR)  |

| 1  | 1  | 1  | 0  | Start Counter Command         | Set Output Port Bits Command   |

| 1  | 1  | 1  | 1  | Stop Counter Command          | Reset Output Port Bits Command |

### Preliminary

### Table 2 REGISTER BIT FORMATS

|              | BIT7              | BIT6                   | BIT5                  | BIT4                                                         | BIT3        | BIT2                | BIT1                         | BITO       |

|--------------|-------------------|------------------------|-----------------------|--------------------------------------------------------------|-------------|---------------------|------------------------------|------------|

| 1            | RX RTS<br>CONTROL | RX INT<br>SELECT       | ERROR<br>MODE         | PARITY M                                                     | ODE         | PARITY<br>TYPE      | BITS PER                     | CHAR.      |

| MR1A<br>MR1B | 0 = no<br>1 = yes | 0 = RXRDY<br>1 = FFULL | 0 = char<br>1 = block | 00 = with pa<br>01 = force p<br>10 = no pari<br>11 = multi-d | arity<br>ty | 0 = even<br>1 = odd | 00 =<br>01 =<br>10 =<br>11 = | = 6<br>= 7 |

| 1404         | BIT7 B                                                              | IT6 | BIT5              | BIT4              | BIT3                                             | BIT2                                             | BIT1                                             | BITO                                             |  |  |

|--------------|---------------------------------------------------------------------|-----|-------------------|-------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--|--|

|              | CHANNEL MOD                                                         | DE  | Tx RTS<br>CONTROL | CTS<br>ENABLE Tx  | STOP BIT LENGTH*                                 |                                                  |                                                  |                                                  |  |  |

| MR2A<br>MR2B | 00 = Normal<br>01 = Auto echo<br>10 = Local loop<br>11 = Remote loo |     | 0 = no<br>1 = yes | 0 = no<br>1 = yes | 0 = 0.563<br>1 = 0.625<br>2 = 0.688<br>3 = 0.750 | 4 = 0.813<br>5 = 0.875<br>6 = 0.938<br>7 = 1.000 | 8 = 1.563<br>9 = 1.625<br>A = 1.688<br>B = 1.750 | C = 1.813<br>D = 1.875<br>E = 1.938<br>F = 2.000 |  |  |

\*Add 0.5 to values shown for 0-7 if channel is programmed for 5 bits/char.

|            | BIT7                   | BIT6              | BIT5              | BIT4              | BIT3              | BIT2              | BIT1              | BITO              |

|------------|------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| CSRA       |                        | RECEIVER CL       | OCK SELECT        |                   |                   | RANSMITTER        | CLOCK SELECT      | г                 |

| CSRB       |                        | See               | text              |                   |                   | See               | text              |                   |

|            | BIT7                   | BIT6              | BIT5              | BIT4              | BIT3              | BIT2              | BIT1              | BITO              |

| CRA        | not used               | MISCEL            | LANEOUS CO        | MMANDS            | DISABLE Tx        | ENABLE Tx         | DISABLE Rx        | ENABLE Rx         |

| CRB        | not used—<br>must be 0 |                   | See text          |                   | 0 = no<br>1 = yes |

|            | BIT7                   | BIT6              | BIT5              | BIT4              | BIT3              | BIT2              | BIT1              | BITO              |

|            | RECEIVED<br>BREAK      | FRAMING<br>ERROR  | PARITY<br>ERROR   | OVERRUN<br>ERROR  | TXEMT             | TxRDY             | FFULL             | RxRDY             |

| SRA<br>SRB | 0 = no<br>1 = yes      | 0 = no<br>1 = yes | 0 = no<br>1 = yes | 0 = no<br>1 = yes | 0 = no<br>1 = yes | 0 = no<br>1 = yes | 0 = no<br>1 = yes | 0 = no<br>1 = yes |

together with bits 4:0. These bits are cleared by a 'reset error status' command. In character mode they are discarded when the corresponding data character is read from the FIFO.

|      | BIT7                     | BIT6                     | BIT5                               | BIT4                               | BIT3                                                       | BIT2        | BIT1                                        | BITO                |

|------|--------------------------|--------------------------|------------------------------------|------------------------------------|------------------------------------------------------------|-------------|---------------------------------------------|---------------------|

|      | OP7                      | OP6                      | OP5                                | OP4                                | OP3                                                        |             | OI                                          | P2                  |

| OPCR | 0 = OPR[7]<br>1 = TxRDYB | 0 = OPR[6]<br>1 = TxRDYA | 0 = OPR[5]<br>1 = RxRDY/<br>FFULLB | 0 = OPR[4]<br>1 = RxRDY/<br>FFULLA | 00 = OPR[3]<br>01 = C/T OU<br>10 = TxCB (1<br>11 = RxCB (1 | TPUT<br>1X) | 00 = OP<br>01 = Tx0<br>10 = Tx0<br>11 = Rx0 | CA (16X)<br>CA (1X) |

|     | BIT7                 | BIT6         | BIT5         | BIT4         | BIT3              | BIT2              | BIT1              | BITO              |  |

|-----|----------------------|--------------|--------------|--------------|-------------------|-------------------|-------------------|-------------------|--|

|     | BRG SET<br>SELECT    |              | COUNTER/TIME |              | DELTA<br>IP3 INT  | DELTA<br>IP2 INT  | DELTA<br>IP1 INT  | DELTA<br>IPO INT  |  |

| CR  | 0 = set1<br>1 = set2 |              | See table 4  |              | 0 = off<br>1 = on |  |

|     | BIT7                 | BIT6         | BIT5         | BIT4         | BIT3              | BIT2              | BIT1              | BITO              |  |

| PCR | DELTA<br>IP3         | DELTA<br>IP2 | DELTA<br>IP1 | DELTA<br>IPO | IP3               | IP2               | IP1               | IPO               |  |

|     | 0 = no               | 0 = no       | 0 = no       | 0 = no       | 0 = low           | 0 = low           | 0 = low           | 0 = low           |  |

Preliminary

# DUAL ASYNCHRONOUS RECEIVER/TRANSMITTER (DUART) SCN2681 SERIES

|     | BIT7                      | BIT6                    | BIT5                    | BIT4              | BIT3                    | BIT2                    | BIT1                    | BITO              |

|-----|---------------------------|-------------------------|-------------------------|-------------------|-------------------------|-------------------------|-------------------------|-------------------|

| R   | INPUT<br>PORT<br>CHANGE   | DELTA<br>BREAK B        | RxRDY/<br>FFULLB        | TxRDYB            | COUNTER<br>READY        | DELTA<br>BREAK A        | RxRDY/<br>FFULLA        | TxRDYA            |

|     | 0 = no<br>1 = yes         | 0 = no<br>1 = yes       | 0 = no<br>1 = yes       | 0 = no<br>1 = yes | 0 = no<br>1 = yes       | 0 = no<br>1 = yes       | 0 = no<br>1 = yes       | 0 = no<br>1 = yes |

|     | BIT7                      | BIT6                    | BIT5                    | BIT4              | BIT3                    | BIT2                    | BIT1                    | BITO              |

| MR  | IN. PORT<br>CHANGE<br>INT | DELTA<br>BREAK B<br>INT | RxRDY/<br>FFULLB<br>INT | TxRDYB<br>INT     | COUNTER<br>READY<br>INT | DELTA<br>BREAK A<br>INT | RxRDY/<br>FFULLA<br>INT | TxRDYA<br>INT     |

|     | 0 = off<br>1 = on         | 0 = off<br>1 = on       | 0 = off<br>1 = on       | 0 = off<br>1 = on | 0 = off<br>1 = on       | 0 = off<br>1 = on       | 0 = off<br>1 = on       | 0 = off<br>1 = on |

|     | BIT7                      | BIT6                    | BIT5                    | BIT4              | BIT3                    | BIT2                    | BIT1                    | BITO              |

| TUR | C/T[15]                   | C/T[14]                 | C/T[13]                 | С/Т[12]           | С/Т[11]                 | C/T[10]                 | C/T[9]                  | C/T[8]            |

|     | BIT7                      | BIT6                    | BIT5                    | BIT4              | BIT3                    | BIT2                    | BIT1                    | BITO              |

| TLR | C/T[7]                    | C/T[6]                  | C/T[5]                  | C/T[4]            | C/T[3]                  | С/Т[2]                  | С/Т[1]                  | C/T[0]            |

cumulation (logical OR) of the status for all characters coming to the top of the FIFO since the last 'reset error' command for channel A was issued.

MR1A[4:3] — Channel A Parity Mode Select — If 'with parity' or 'force parity' is selected, a parity bit is added to the transmitted character and the receiver performs a parity check on incoming data. MR1A[4:3] = 11 selects channel A to operate in the special multidrop mode described in the Operation section.

MR1A[2] — Channel A Parity Type Select — This bit selects the parity type (odd or even) if the 'with parity' mode is programmed by MR1A[4:3], and the polarity of the forced parity bit if the 'force parity' mode is programmed. It has no effect if the 'no parity' mode is programmed. In the special multidrop mode it selects the polarity of the A/D bit.

MR1A[1:0] — Channel A Bits per Character Select — This field selects the number of data bits per character to be transmitted and received. The character length does not include the start, parity, and stop bits.

### MR2A — Channel A Mode Register 2

MR2A is accessed when the channel A MR pointer points to MR2, which occurs after any access to MR1A. Accesses to MR2A do not change the pointer.