## **8K RAM BOARD**

© 1977

| FEATURES                                                                                                                                                                                                                                                       | PARTS LIST                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Plug compatible with the ALTAIR<br/>8800 and IMSAI 8080, or any<br/>other system using the "ALTAIR<br/>bus."</li> <li>CLow-power, 500 nanosecond<br/>RAMs. No wait cycles required.</li> </ul>                                                        | <pre>1 PC Board with gold fingers<br/>69 16 pin low-profile sockets<br/>3 14 pin low-profile sockets<br/>2 7 position DIP switches<br/>65 91L02APC/D2102AL-4 low-<br/>power RAMs<br/>1 74LS00</pre> |

| <ul> <li>OLow-power Schottky support<br/>chips.</li> <li>ODIP switch selection of memory<br/>address assignment and wait<br/>cycles.</li> <li>OMemory protect can be set for</li> </ul>                                                                        | 1 7402<br>1 74LS42<br>1 74LS74<br>2 74367 (DM 8097)<br>1 DM 8131<br>4 7805 or 340T-5 regulators<br>2 2.7 uF/ 20V tantalums<br>4 0.1 uF disc capacitors<br>14 2.7K ohm, ‡W resistors                 |

| <ul> <li>ordening protocol can be been for<br/>increments of 256 bits, 512<br/>bits, 1K, 2K, 4K or 8K by DIP<br/>switch.</li> <li>OT.I. low profile sockets pro-<br/>vided for all RAMs and ICs.</li> <li>OGold plated edge connector<br/>contacts.</li> </ul> | 2 39K, ±W resistors<br>4 sets #6 screws, nuts and<br>washers<br>1 instruction set                                                                                                                   |

2102A walsh ave. santa clara, ca. 95050 408/ 246-2707

4) Add jpr 1 for SOL mainframes only.

2102A Walsh Avenue SANTA CLARA, CALIFORNIA 95050

(408) 246-2707

MB6A- 8K STATIC MEMORY BOARD

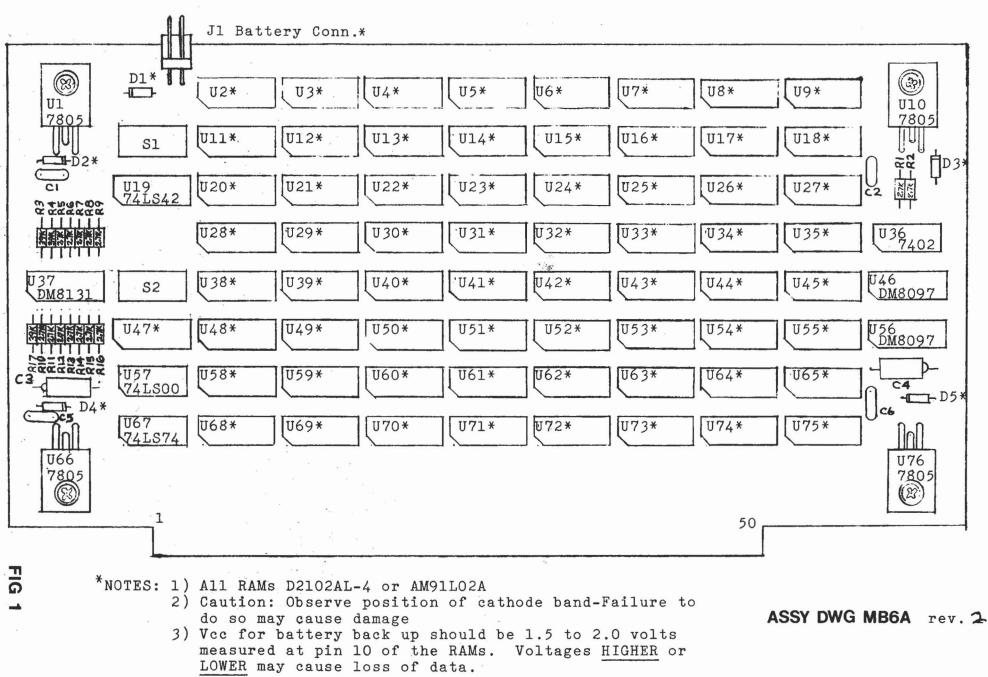

| 1.0 ASSEMBLY INSTRUCTIONS (refer to Figure 1)                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Check kit contents against parts list.                                                                                                                                                                                                                                                                                                                          |

| Check PC board for possible warpage and straighten if required.                                                                                                                                                                                                                                                                                                 |

| Insert 69 sixteen-pin sockets into the component side of the<br>board with the "pin 1" index toward the <b>top</b> of the board.<br>(The component side is the side on which "Solid State Music"<br>is printed.)                                                                                                                                                |

| Insert 3 fourteen-pin sockets. DON'T SOLDER!                                                                                                                                                                                                                                                                                                                    |

| Place a flat piece of stiff cardboard of appropriate size on<br>top of the sockets to hold them in place.                                                                                                                                                                                                                                                       |

| Holding the cardboard in place against the sockets, turn the<br>board over and lay it on a flat surface. (Be sure that all<br>of the sockets pins are through the holes.)                                                                                                                                                                                       |

| Note: Keep soldering iron tip clean to prevent rosin and<br>sludge from being deposited on traces. Wipe tip frequently<br>on a damp cloth or steel wool.                                                                                                                                                                                                        |

| On each socket, solder two of the corner pins, choosing two that are diagonally opposite of each other.                                                                                                                                                                                                                                                         |

| Once the sockets are secured, lift the board and check to see<br>if they are flat against the board. If not, seat the sockets<br>by pressing on top while reheating each soldered pin.                                                                                                                                                                          |

| Complete soldering the remaining pins of each socket. Touch<br>pin and pad with iron tip, allowing enough solder to flow to<br>form a filet between pin and pad. Keep the tip against the<br>pin and pad just long enough to produce the filet. Too much<br>heat can cause separation of pad and trace from the board.<br>A 600 degree iron tip is recommended. |

| Observing polarity, insert and solder the tantalum caps.                                                                                                                                                                                                                                                                                                        |

| Insert and solder the 4 disc capacitors.                                                                                                                                                                                                                                                                                                                        |

| Insert DIP switches with the word "OPEN" toward the bottom of the board. Solder.                                                                                                                                                                                                                                                                                |

| Place regulators on the board so the mounting hole in the re-<br>gulator is in line with the hole in the board. Mark leads for<br>proper bending position to match the board holesallow for a<br>bend radius.                                                                                                                                                   |

2102A Walsh Avenue SANTA CLARA, CALIFORNIA 95050 (408) 246-2707

1.0 ASSEMBLY (continued)

Bend regulator leads to match holes in board.

If available, apply thermal compound to the back side of each regulator case (the part that lies flat against the board).

Drop regulators in place on front of board, insert #6 screws from front, and secure firmly with lock washer and nut.

Solder regulator leads to pads on back of board. Do not use excessive heat.

📉 Insert and solder the 14 2.7K ohm and 3 39K ohm resistors. 🗡

Insert and solder 5 diodes (observing polarity) and molex battery connector.

Apply power (+8 volts approx.) to board by plugging into computer or by connection from a suitable power supply and measure the regulated output of each regulator. If less than 4.8 volts is measured (allowing for meter accuracy) check for shorts or wiring errors. CAUTION! WHILE IT HAS NEVER HAPPENED TO US, SHORTED REGUALTORS HAVE BEEN KNOWN TO EXPLODE WITH POSSIBLE INJURY TO EYES OR HANDS WHILE BEING TESTED. BETTER SAFE THAN SORRY - KEEP FACE AND HANDS CLEAR OF THE REGULATOR SIDE OF THE BOARD DURING THIS AND SUBSEQUENT TESTS!

\_\_\_\_\_Insert the following ICs in their sockets: U19, U36, U37, U46, U47 (a91L02APC), U56, U57, and U67. Be sure all pins are seated in the sockets. Repeat voltage checks.

2.0 FUNCTIONAL CHECK

WARNING! DO NOT INSTALL OR REMOVE BOARD WITH POWER ON. DAMAGE TO THIS AND OTHER BOARDS COULD OCCUR.

Install the first 2K of 91LO2As (U2 through U9 and U11 through U18). Be sure pins are seated in sockets.

\_\_\_\_Set S1 as follows:

All and Al2 -- open Al3 and Al5 -- closed 2K and 4K -- open

2102A Walsh Avenue SANTA CLARA, CALIFORNIA 95050 (408) 246-2707

| 2.0 | O FUNCTIONAL CHECK (continued)                                                                                                                      |                                                                              |                                              |               |                       |                                 |       |                                 |                                      |                                      |                                                  |                                  |                                  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------|---------------|-----------------------|---------------------------------|-------|---------------------------------|--------------------------------------|--------------------------------------|--------------------------------------------------|----------------------------------|----------------------------------|

|     | Set S2 as follows:                                                                                                                                  |                                                                              |                                              |               |                       |                                 |       |                                 |                                      |                                      |                                                  |                                  |                                  |

|     | 4k, 2k, 1k, 512, 256, and Tl open<br>T2 closed                                                                                                      |                                                                              |                                              |               |                       |                                 |       |                                 |                                      |                                      |                                                  |                                  |                                  |

|     | The above switch positions set the following conditions:                                                                                            |                                                                              |                                              |               |                       |                                 |       |                                 |                                      |                                      |                                                  |                                  |                                  |

|     | Memo:<br>Memo:                                                                                                                                      | ry Comp<br>ry Prot                                                           | 0000-1FF<br>lement -<br>ect Incr<br>Cycles   | - 8K<br>ement | ; 8                   |                                 | ough  | 037.                            | -377                                 | octa                                 | al)                                              |                                  |                                  |

|     | sett:<br>addr                                                                                                                                       | ing, mu                                                                      | rd. Rem<br>st have<br>or the f               | the f         | irst                  | 8K u:                           | ncont | teste                           | ed.                                  | Any                                  | boar                                             | rds                              |                                  |

|     |                                                                                                                                                     | mine" a<br>ions.                                                             | t octal                                      | 000 0         | 000, v                | erif                            | y pro | otec                            | t/unj                                | prote                                | ect d                                            | con-                             |                                  |

|     |                                                                                                                                                     | mine" a<br>ions.                                                             | t octal                                      | 007 3         | 877, v                | erif                            | y pro | otec                            | t/unj                                | prote                                | ect o                                            | con-                             |                                  |

|     | Manually program with the front panel switches to verify<br>that data can be stored. Don't forget to unprotect the<br>memory before you do this.    |                                                                              |                                              |               |                       |                                 |       |                                 |                                      |                                      |                                                  |                                  |                                  |

|     |                                                                                                                                                     | at the<br>tional.                                                            | above st                                     | eps u         | intil                 | all a                           | 8K ha | ave 1                           | been                                 | ver                                  | ified                                            | l as                             |                                  |

|     | If you're set up to BASIC, it is an excellent dynamic test<br>of your memory system. Be sure that all memory in the<br>system has been unprotected. |                                                                              |                                              |               |                       |                                 |       |                                 |                                      |                                      |                                                  |                                  |                                  |

| 3.0 | SET-                                                                                                                                                | UP                                                                           |                                              |               |                       |                                 |       |                                 |                                      | 36                                   |                                                  |                                  |                                  |

|     | 3.1                                                                                                                                                 | ADDRES                                                                       | S SELECT                                     | ION (         | Sl)                   |                                 |       |                                 |                                      |                                      |                                                  |                                  |                                  |

|     |                                                                                                                                                     |                                                                              | s Range<br>ex                                |               | igh 0<br>5 Al4        |                                 |       |                                 |                                      |                                      |                                                  |                                  |                                  |

|     | 8K<br>16K<br>24K<br>32K<br>40K<br>48K<br>56K<br>64K                                                                                                 | 0000 -<br>2000 -<br>4000 -<br>6000 -<br>8000 -<br>A000 -<br>C000 -<br>E000 - | 3FFF<br>5FFF<br>7FFF<br>9FFF<br>BFFF<br>DFFF |               | 0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0 |       | 0<br>0<br>0<br>0<br>0<br>0<br>0 | ON<br>ON<br>OFF<br>OFF<br>OFF<br>OFF | ON<br>OFF<br>OFF<br>ON<br>OFF<br>OFF | ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF | ON<br>ON<br>ON<br>ON<br>ON<br>ON | ON<br>ON<br>ON<br>ON<br>ON<br>ON |

|     |                                                                                                                                                     |                                                                              |                                              |               |                       |                                 |       |                                 |                                      |                                      |                                                  |                                  |                                  |

-5-

2102A Walsh Avenue SANTA CLARA, CALIFORNIA 95050 (408) 246-2707

## 3.0 SET-UP (continued)

## 3.2 MEMORY COMPLEMENT SELECTION

| Memory | Complement | DIP Switches<br>2K 4K |     |  |  |  |

|--------|------------|-----------------------|-----|--|--|--|

|        | 2K         | ON                    | ON  |  |  |  |

|        | 4K         | ON                    | OFF |  |  |  |

|        | 8K         | OFF                   | OFF |  |  |  |

Note: The 2K switch activates address line All The 4K switch activates address line Al2

## 3.3 MEMORY PROTECT INCREMENTS (S2)

| Protect Increments | DIP Switch |     |     |     |           |  |  |

|--------------------|------------|-----|-----|-----|-----------|--|--|

|                    | 256        | 512 | 1K  | 2K  | <u>4K</u> |  |  |

| 256                | ON         | ON  | ON  | ON  | ON        |  |  |

| 512                | OFF        | ON  | ON  | ON  | ON        |  |  |

| lK                 | OFF        | OFF | ON  | ON  | ON        |  |  |

| 2K                 | OFF        | OFF | OFF | ON  | ON        |  |  |

| 4 K                | OFF        | OFF | OFF | OFF | ON        |  |  |

| 8K                 | OFF        | OFF | OFF | OFF | OFF       |  |  |

Note: Switch arrangements other than those shown above provide other protect patterns.

#### 3.4 MEMORY WAIT CYCLES

| RAM Access Time                                         | DIP Swit               | ch               | Wait Cycles    |

|---------------------------------------------------------|------------------------|------------------|----------------|

|                                                         | <u>T1</u>              | T2               |                |

| less than 550 ns<br>550ns to 1050ns<br>1050ns to 1550ns | DONT CARE<br>ON<br>OFF | ON<br>OFF<br>OFF | none<br>1<br>2 |

#### 4.0 TROUBLE SHOOTING HINTS

- a. Check for proper settings of DIP switches.

- b. Verify that all ICs are in the correct sockets.

- c. Visually inspect all ICs to be sure that leads are in the sockets and not bent under.

- d. Verify that the output voltage of each regulator is within 4.7 to 5.3 volts.

2102A Walsh Avenue SANTA CLARA, CALIFORNIA 95050 (408) 246-2707

## 4.0 TROUBLE SHOOTING HINTS (continued)

- e. Inspect back side of board for solder bridges, running a small sharp knife blade between traces that appear suspicious. A magnifying glass is a must for this.

- f. Be sure all memory has been unprotected.\*

- g. If you can't protect/unprotect memory:

(1) recheck address settings

(2) check U36 (7402)

- h. If you have an addressing problem:

(1) check U19 (74LS42) for addresses Al0 thru A12.

(2) check U37 (DM8131) for addresses A13 thru A15.

- i. If you have a problem with data output (consistent missing bits):

- (1) check U46 (DM8097) for bits 0 through 3.

- (2) check U56 (DM8097) for bits 4 through 7.

- (3) check U36 (7402) for all bits.

- j. If you have a wait cycle problem:(1) check U57 (74LS00) and U67 (74LS74).

\*NOTE (IMSAI & Poly users): If you have not incorporated a protect/unprotect feature into your mainframe, we recommend removing U47 (protect memory) of the MB6 to insure reliable operation, as the memory can come up protected when power is turned on (if U47 is not removed)

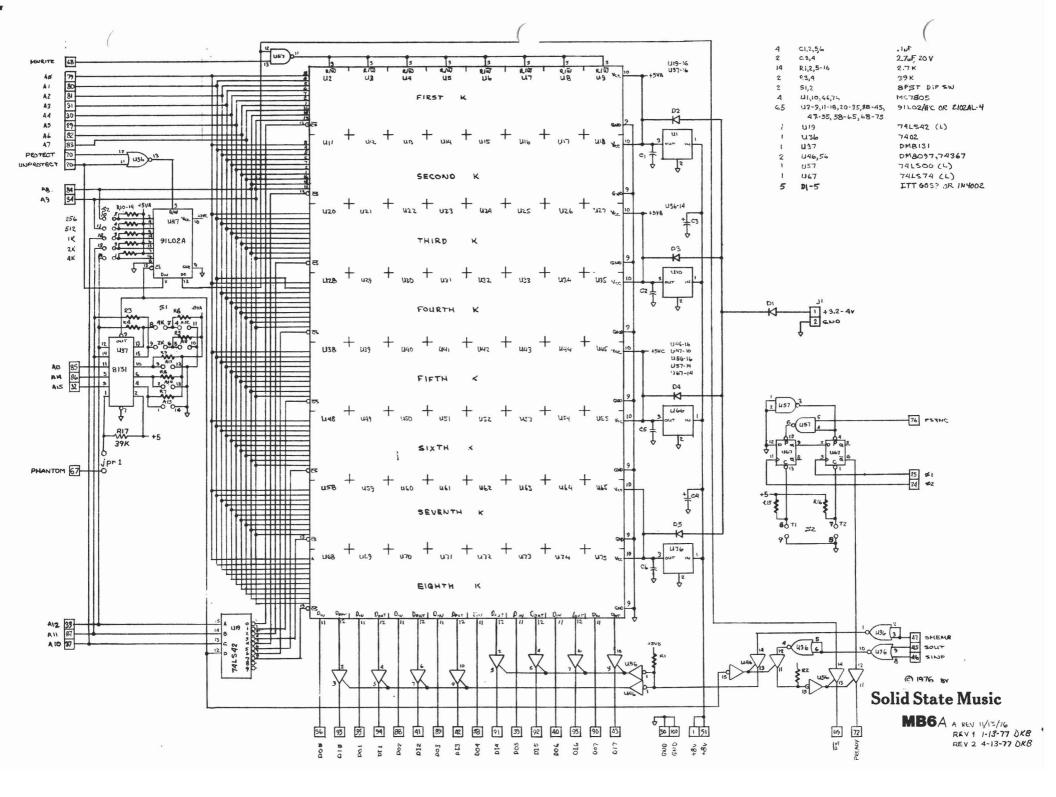

## 5.0 THEORY OF OPERATION

5.1 GENERAL

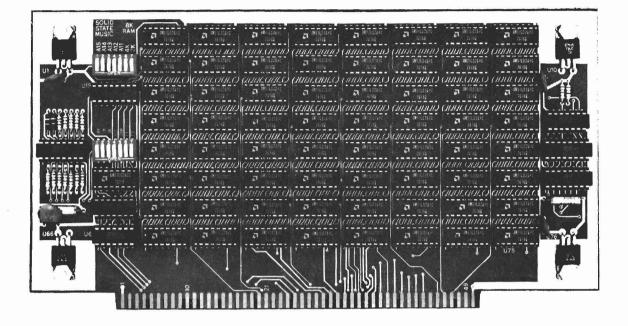

The MB6 is an 8K-byte (8K x 8 bit) random access memory featuring:

\* Selectable address \* Memory protect in selectable increments (from ¼K to 4K) \* Selectable memory wait cycles (from 0 to 2) \* Extra low-power, 500ns RAMs \* Low-power, Schottky support chips

The memory chips employed are AMD 91L02A or NEC 2102AL-4 lK x l bit, static RAMs. The RAM chips are organized in an 8 row x 8 column matrix. Each column corresponds to one bit of the memory word and contains 8K bits of memory.

2102A Walsh Avenue SANTA CLARA, CALIFORNIA 95050 (408) 246-2707

### 5.0 THEORY OF OPERATION (continued)

#### 5.2 DATA LINES

The data inputs (Di) of all the RAMs in each column are bussed together and connected to the 8 CPU output lines (DO  $\emptyset$  thru DO 7) and the data outputs (Do) are bussed together and connected to the 8 CPU input lines (DI  $\emptyset$ thru DI 7). The bussing of output lines is made possible by the tri-state outputs of the RAMs. These output lines are buffered by tri-state buffers.

#### 5.3 ROW ADDRESSING

Address lines AlO thru Al2 are decoded by U19, a 4 to 10 line decoder. The decoders' output enables one of 8 rows of RAMs by activating the chip select lines of all the RAMs in one row. (The fourth line of the decoder is used only as an overall memory enable line, and the last 2 outputs are unused.)

#### 5.4 RAM CELL ADDRESS

The 10 address lines on each chip are all bussed together and are fed directly by address lines AO thru A9. These lines select a particular bit in each of the 64 RAMs.

#### 5.5 BOARD ADDRESS

Address lines A13 thru A15 select a particular 8K block of memory. The address of the MB6 is user selected by switches A13 thru A15. If the address on lines A13 thru A15 matches the preselected address of the board, comparator U37 enables protect memory U47 and decoder U19, and unlocks the SMEMR, SOUT, and SINP signals (through pin 15 of U46). NOTE\* If only 2K or 4K of memory are being used, address lines A12 and A11 may be assigned to the address of the board as required by closing switches 4K and 2K. This enables address selection switches A12 &/or A11 as well.

#### 5.6 MEMORY PROTECT

Only one row of the protect memory U47 is used to retain protect status for the board. If all S2 positions are open, a single bit in the memory determines protect status for all 8K of memory. Assuming the protect memory has been activated ( $\overline{CS}=0$ ) by a correct memory address input to comparator U37, activating the protect (unprotect) line writes a 0 (1) into the protect memory. The output

2102A Walsh Avenue SANTA CLARA, CALIFORNIA 95050 (408) 246-2707

#### 5.0 THEORY OF OPERATION (continued)

5.6 (continued)

is fed to a gate which disables (for protect) or enables (for unprotect) the MWRITE line. The output of the protect memory is also fed to a buffer whose output is the Protect Status (PS) line.

Memory protect increments of less than 8K maybe selected by closing S2 positions as required; thereby assigning those address lines (A8 thru Al2) desired to address various bits in the protect memory. In this way, protect increments from  $\frac{1}{2}$ K to 4K maybe implemented.

Dual-D flip flop U67 is used to set the number of wait cycles the CPU goes through when reading or writing data on this board. It signals that it is ready to read or write by actuating the Ready line (PREADY).

Because 500ns RAMs are supplied with the MB6, no wait cycles are normally required. Therefore, T2 should be closed which clears the second DFF and maintains the Ready line in a high state.

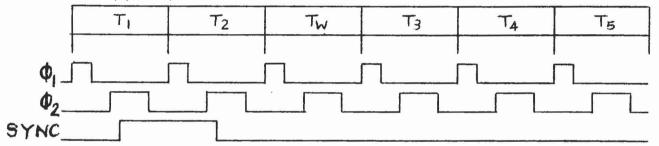

If 1 wait cycle is desired, T2 should be open and T1 closed. This causes the output of DFF #1 to follow the SYNC pulse. Because its output is high until after the second Ø1 clock pulse in the Machine Cycle, the Ready line (Q of DFF #2) does not go high until after the third Ø2 clock pulse occurs. Therefore the third state in the machine cycle becomes a wait state. NOTE\* The CPU looks for the Ready flag on the third Ø1 clock pulse of the Machine Cycle. If the Ready flag has not been raised, the CPU waits until the Ø1 clock and Ready flag occur concurrently.

If 2 wait cycles are desired, T1 & T2 should both be open. This causes Q of DFF #1 to go high at the start of SYNC, but it does not go low until the third  $\emptyset$ 2 clock pulse occurs. Therefore, 2  $\emptyset$ 1 clock pulses are skipped before the Ready flag is raised

2102A Walsh Avenue SANTA CLARA, CALIFORNIA 95050 (408) 246-2707

### 5.0 THEORY OF OPERATION (continued)

### 5.8 MISCELLANEOUS FLAGS

The Memory Read line (SMEMR) is used to enable the tristate buffers on the output lines. The Input (SINP) and Output (SOUT) lines are ORed together and the result is used to disable the flag output buffers (PS & PREADY flags) when the bus is being used for I/O.

### 6.0 WARRANTY

Parts guaranteed to original purchaser for 90 days, unless failure is due to misuse or failure of purchaser to excercise caution in assembly and operation. Registration card must be returned at time of purchase to validate warranty.

Assembled boards may be returned for service. A service charge will be made unless, in our judgement, the problem is due to a defective board or parts.

Our address: CYBERCOM/2102A Walsh Ave./ Santa Clara, Ca. 95050

2102A Walsh Avenue SANTA CLARA, CALIFORNIA 95050 (408) 246-2707

## ADDENDUM FOR SOL USERS

## SOL "PHANTOM"

The SOL system requires that the first block of memory is disabled for the first few machine cycles after power up in order to allow the monitor to initialize the system.

The RAM is disabled by means of the "Phantom" signal on pin 67 of the bus. This feature may be incorporated on the MB6 simply by adding jumper jpr 1.