#### Soldering PC Boards

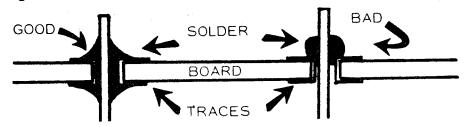

Two common causes of trouble with PC boards are bad solder joints or solder bridges. Usually, bad solder joints are caused by either a cold solder joint or contamination. A good solder joint is characterized by a bright shiny and smooth surface ( see figure 1).

Figure 1. CROSS-SECTION OF A PC BOARD SHOWING GOOD AND BAD SOLDER CONNECTIONS

A cold solder joint is characterized by a dull surface and usually a lumpy or balled appearance. It takes practice and patience to obtain a good solder joint consistently. However, the first step is to apply flux to all connections before the solder. Second, heat the connection for a second or two with the soldering iron. Third, apply solder to the opposite side of the connection. Don't touch the solder to the iron. Flux has a "wetting" effect on solder which causes the solder to flow smoothly, completely filling the connection. If flux is not used or the metal around the connection is contaminated (dirty) it is almost impossible to have a good solder joint.

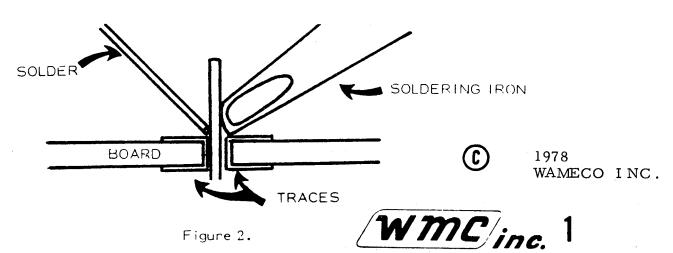

Solder bridges are usually caused by using a soldering iron tip that's too large, solder wire that's too large, or trying to rush the job. Use a small spade tip iron (see figure 2). Touch the connection with the flat side of the tip. After the flux bubbles, touch the solder to the opposite side of the connection. Again, don't touch the solder to the iron. The connection is hot enough to melt the solder causing it to flow around the connection. Do not use too much solder. Use a little and watch it flow. Solder is like spice for cooking, don't use too much.

Applying heat for extended periods will cause either or both of the following: the trace or pad will lift from the board or the board material will turn brown. Remove the iron before this happens. One hobbyist counts the bubbles that pop in the solder. He found seven to nine bubbles insured good solder flow without over heating.

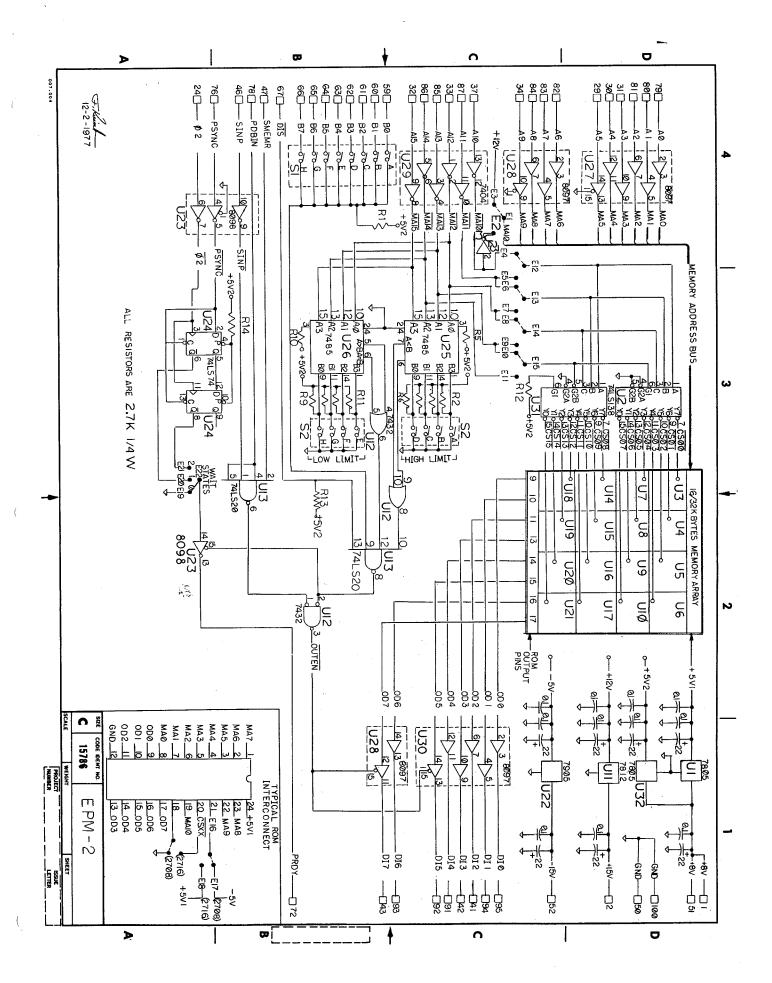

The EPM-2 is a memory board designed to interface programmed 2708's or 2716's to the S-100 (WAMECO<sub>TM</sub>) bus(see Tables I and II). Provisions have been made for multiple wait states, memory addressing options and phantom disable. Any multiple of one memory chip can be used in the board and the board start and stop address can be set in 4 K Byte boundaries anywhere in the 65 K Byte memory of your computer. If 4 K Bytes or less, the board can be configured to occupy only the amount of 4 K Bytes in the memory map of your computer. This selection can be increased by 4 K Byte increments until the full 16 K is selected for the 2708 configuration and 32 K for the 2716 configuration. The board is designed to use the single voltage 2716 memory chip.

#### Parts List

| Quantity | Part                                     |

|----------|------------------------------------------|

| 7        | 22 $\mu$ F 20V Tantalum capacitor        |

| 24       | .1 $\mu$ F ceramic disc capacitors       |

| 14       | 2.7 K $\Omega$ 1/4 Watt carbon resistors |

|          | 7805, 309T-5, 340T-5                     |

|          | 74LS138                                  |

|          | 2708 or INTEL 2716                       |

| 1        | 7812 or 340T-12                          |

| 1        | 7432                                     |

| 1        | 74LS20                                   |

| 1        | 7905 or LM320T-5                         |

| 1        | 8098 or 74368                            |

| 1        | 74LS74                                   |

| . 2      | 7485                                     |

| 3        | 8097 or 74367                            |

| 1        | 7404                                     |

| 2        | 8 position dip switches                  |

| 4        | 14 pin low profile sockets               |

| 8        | 16 pin low profile sockets               |

| 16       | 24 pin low profile sockets               |

| 4        | Aham #361 heat sinks                     |

| 23       | l" jumper wires                          |

| 1        | insulating washer                        |

|          | 7 24 14 2 2 16 1 1 1 1 2 3 1 2 4 8 16 4  |

## Tools or supplies needed to assemble and test EPM-2

```

1

Q Tip cotton swab

pair needle nose pliers

1

1

pair diagonal cutting pliers

1

bottle rosin flux

1

tube silicone thermal compound

1

jar solder cleaner

1

roll solder wick

1

Phillips screwdriver

small adjustable wrench or socket to fit regulator nut

1

roll (.031" or .040") SN60/40 rosin core solder

1

1

25 to 40 W soldering iron with small spade tip

1

strong light

1

magnifying glass

XACTO knife with number 16 blade

1

1

multimeter with leads

power supply with variable outputs

computer w/RAM Memory board

```

# S-100 (WAMECO) BUS DESCRIPTION

| 1                                                        | +5V          |                                      |

|----------------------------------------------------------|--------------|--------------------------------------|

| 2                                                        | +15V         |                                      |

| 2<br>3<br>4                                              | XRDY         | X                                    |

| 4                                                        | VIØ          | X<br>X<br>X<br>X<br>X<br>X<br>X      |

|                                                          | 7771         | $\frac{\Lambda}{\nabla}$             |

| 5<br>6                                                   | V11          | <del>-</del>                         |

| 7                                                        | V12          | <del>- </del>                        |

|                                                          | V13          | $\frac{X}{X}$                        |

| 8                                                        | VI4          | X                                    |

| 9                                                        | VI5          | X                                    |

| 10                                                       | VI6          | X                                    |

| 11                                                       | VI7          | X                                    |

| 12                                                       |              |                                      |

| 13                                                       |              |                                      |

| 14                                                       |              |                                      |

| 15                                                       |              |                                      |

| 16                                                       |              |                                      |

| 17                                                       |              |                                      |

| 18                                                       | STAT DISABLE | <del></del>                          |

| 10                                                       | SIAI DISABLE | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X |

| 19                                                       | CIC DISABLE  | - <del></del>                        |

| 20                                                       | UNPROTECT    | <u>X</u> _                           |

| 21                                                       | SS           | X                                    |

| 22                                                       | ADDR DSBL    | X                                    |

| 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29 | DO DSBL      | X                                    |

| 24                                                       | 02           | X                                    |

| 25                                                       | Ø1<br>PHLDA  | X                                    |

| 26                                                       | PHLDA        | X                                    |

| 27                                                       | PWAIT        |                                      |

| 28                                                       | PINTE        |                                      |

| 20                                                       | A5           |                                      |

| 27                                                       | A4           |                                      |

| 30                                                       | A4           |                                      |

| 31                                                       | A3<br>A15    |                                      |

| 32                                                       | A15          |                                      |

| 33                                                       | A12          |                                      |

| 34                                                       | A 9          |                                      |

| 35                                                       | DO1          | X                                    |

| 36                                                       | DOØ          | X                                    |

| 37                                                       | A10          |                                      |

| 38                                                       | DO4          | X                                    |

| 39                                                       | DO5          | X                                    |

| $\frac{3}{40}$                                           | DO6          | X<br>X<br>X<br>X                     |

| $\frac{30}{41}$                                          | DI2          | $\overline{\mathbf{x}}$              |

| 42                                                       | DI3          | X                                    |

|                                                          | D12          | X                                    |

| 43                                                       | DI7          |                                      |

| 44                                                       | SMI          |                                      |

| 45                                                       | SOUT         |                                      |

| 46                                                       | SINP         |                                      |

| 47                                                       | SMEMR        |                                      |

| 48                                                       | SHLTA        |                                      |

| 49                                                       | CLOCK (2MHz) |                                      |

| 50                                                       | GND          |                                      |

|                                                          | MNEMONIC     | TERM                                 |

|                                                          | ·            | •                                    |

| 51                                                          | +5V      | A                    | 1                                                |

|-------------------------------------------------------------|----------|----------------------|--------------------------------------------------|

| 51                                                          | -15V     | В                    |                                                  |

| 53                                                          | SSW DSB  | $\overline{c}$       |                                                  |

| 53<br>54                                                    | EXT CLR  | $\frac{\ddot{D}}{D}$ | X                                                |

| 54                                                          | EVICTE   | E                    |                                                  |

| 55                                                          |          |                      |                                                  |

| 56                                                          |          | F                    |                                                  |

| 57                                                          |          | H                    |                                                  |

| 58                                                          |          | J                    |                                                  |

| 59                                                          |          | K                    |                                                  |

| 60                                                          |          | L                    |                                                  |

| 61                                                          |          | M                    |                                                  |

| 62                                                          |          | N                    |                                                  |

| 63                                                          |          | P                    |                                                  |

| 64                                                          |          | R                    |                                                  |

|                                                             |          | S                    |                                                  |

| 65                                                          |          | T                    |                                                  |

| 66                                                          |          |                      |                                                  |

| 67                                                          | PHANTOM  | Ü                    |                                                  |

| 68                                                          | MWRITE   | V                    | X                                                |

| 69                                                          | PS       | W                    |                                                  |

| 70                                                          | PROTECT  | X                    | X                                                |

| $\begin{array}{r} 71 \\ \hline 72 \\ \hline 73 \end{array}$ | RUN      | Y                    | X                                                |

| $\frac{1}{72}$                                              | PRDY     | Z                    | X                                                |

| 73                                                          | PINT     | a                    | X                                                |

| 1 7 4                                                       | PHOLD    | Ъ                    | X                                                |

| $\frac{74}{75}$                                             | PRESET   |                      | <del>                                     </del> |

| 75                                                          |          | С                    | X<br>X<br>X                                      |

| 76                                                          | PSYNC    | d                    | <b>├</b>                                         |

| 77                                                          | PWR      | е                    | A                                                |

| 78                                                          | PDBIN    | f                    | X                                                |

| 79                                                          | ΑØ       | h                    | 11                                               |

| 80                                                          | Al       | j                    |                                                  |

| 81                                                          | A2       | k                    |                                                  |

| 82                                                          | A6       |                      |                                                  |

| 83                                                          | A7       | m                    | 1                                                |

| $8\frac{3}{4}$                                              | A8       | n                    | <del> </del>                                     |

|                                                             |          |                      | <del> </del>                                     |

| 85                                                          | A13      | P                    | <del> </del>                                     |

| 86                                                          | A14      | r                    | <b>├</b> ──┤                                     |

| 87                                                          | All      | S                    | <b> </b>                                         |

| 88                                                          | DO2      | t                    | X                                                |

| 89                                                          | DO3      | u                    | X                                                |

| 90                                                          | DO7      | V                    | X                                                |

| 91                                                          | DI4      | w                    | X<br>X<br>X<br>X                                 |

| 92                                                          | DI5      | x                    | X                                                |

| $\frac{72}{93}$                                             | DI6      | У                    | x                                                |

| $\frac{73}{04}$                                             | DII      | Z                    | X                                                |

| $\frac{94}{95}$                                             | DIA      | AA                   | $\frac{X}{X}$                                    |

| 95                                                          | DIØ      |                      |                                                  |

| 96                                                          | SINTA    | AB                   | <del>  </del>                                    |

| 97                                                          | SWO      | AC                   |                                                  |

| 98                                                          | SSTACK   | AD                   |                                                  |

| 99                                                          | POC      | AÉ                   |                                                  |

| 100                                                         |          | AF                   |                                                  |

| PIN                                                         | MNEMONIC | ALTER.               | TERM                                             |

| T TT.                                                       | 1        | PIN                  | 1                                                |

|                                                             |          | DESIG.               | 1                                                |

|                                                             |          | · DIOIG.             | •                                                |

| Pin#     | Mnemonic                      | Enabled State | Description                                                 |

|----------|-------------------------------|---------------|-------------------------------------------------------------|

| 1        | +8 Volts                      | NA            | Unregulated +8 Volts DC.                                    |

|          |                               |               | This voltage should not be                                  |

|          |                               |               | <pre>less than +8 or greater than +11 volts.</pre>          |

| 2        | +16 Volts                     | NA            | Unregulated +16 Volts DC.                                   |

|          |                               | • • • •       | This voltage should not be                                  |

|          |                               |               | less than +16 or greater                                    |

|          |                               |               | than +20 Volts.                                             |

| 3.       | XRDY                          | Low           | Causes CPU to enter WAIT                                    |

| 4        | 1777                          | Tav           | state when enabled.                                         |

| 4        | <u>VIO</u><br><u>VII</u>      | Low<br>Low    | Vectored Interrupt priority 0 Vectored Interrupt priority 1 |

| 5        | $\frac{\sqrt{11}}{\sqrt{12}}$ | Low           | Vectored Interrupt priority 2                               |

| 7        | <u>V13</u>                    | Low           | Vectored Interrupt priority 3                               |

| 8        | VI4                           | Low           | Vectored Interrupt priority 4                               |

| 9        | VI5                           | Low           | Vectored Interrupt priority 5                               |

| 10       | VI6                           | Low           | Vectored Interrupt priority 6                               |

| 11       | VI7                           | Low           | Vectored Interrupt priority 7                               |

| 12       |                               | NA            | Not used                                                    |

| 13       |                               | NA            | Not used                                                    |

| 14<br>15 | ; <b></b>                     | NA<br>NA      | Not used<br>Not used                                        |

| 16       |                               | NA            | Not used                                                    |

| 17       |                               | NA<br>NA      | Not used                                                    |

| 18       | STAT DISABLE                  |               | The eight status line buffers                               |

|          |                               |               | on the CPU board enter the                                  |

|          |                               |               | high impedance state when                                   |

|          | ·                             | _             | enabled.                                                    |

| 19       | C/C DISABLE                   | Low           | The six command/control line buffers on the CPU board       |

|          |                               |               | enter the high impedance                                    |

|          |                               |               | state when enabled.                                         |

| 20       | UNPROTECT                     | High          | Combined with address in an                                 |

|          |                               | 8             | AND gate on a memory board                                  |

|          |                               |               | which causes the PROTECT                                    |

|          |                               |               | flip-flop to be cleared.                                    |

| 21       | SS                            | High          | Indicates the CPU is single                                 |

|          | ADDR DSBL                     | Low           | stepping. The 16 address line buffers                       |

| 22       | ADDK DSDL                     | LOW           | on the CPU board enter the                                  |

|          |                               |               | high impedance state when                                   |

|          |                               |               | enabled.                                                    |

| 23       | DO DSBL                       | Low           | The eight data-out lines on                                 |

|          |                               |               | the CPU board enter the high                                |

|          | 4 -                           |               | impedance state when enabled.                               |

| 24       | Ø 2                           | High          | Buffered TTL CPU phase 2                                    |

| 25       | <b>A</b> 1                    | Uiah          | clock.<br>Buffered TTL CPU phase l                          |

| 25       | <b>Ø</b> 1                    | High          | clock.                                                      |

| 26       | PHLDA                         | High          | CPU board "Hold Acknowledge                                 |

|          | * * * * * * *                 |               | to HOLD-H input.                                            |

| 27       | PWAIT                         | High          | CPU output showing a WAIT                                   |

|          |                               | _             | state is occuring.                                          |

|          |                               | Figure 3B.    |                                                             |

| Pin# | Mnemonic   | Enabled State     | Description                    |

|------|------------|-------------------|--------------------------------|

| 28   | PINTE      | High              | CPU output showing that        |

|      |            | _                 | Interrupts are enabled.        |

| 29   | A5         | High              | Address Bit 5                  |

| 30   | A4         | High              | Address Bit 4                  |

| 31   | A3         | High              | Address Bit 3                  |

| 32   | A15        | High              | Address Bit 15                 |

| 33   | A12        | High              | Address Bit 12                 |

| 34   | A 9        | High              | Address Bit 9                  |

| 35   | DO1        | High              | CPU Data Out Bit 1             |

| 36   | DO0        | High              | CPU Data Out Bit 0             |

| 37   | A10        | High              | Address Bit 10                 |

| 38   | DO4        | High              | CPU Data Out Bit 4             |

| 39   | DO5        | High              | CPU Data Out Bit 5             |

| 40   | DO6        | High              | CPU Data Out Bit 6             |

| 41   | D12        | High              | Data In Bit 2 to CPU           |

| 42   | D13        | High              | Data In Bit 3 to CPU           |

| 43   | D17        | High              | Data In Bit 7 to CPU           |

| 44   | SM1        | High              | CPU output indicating it is    |

|      |            | S                 | performing Fetch Instruction.  |

| 45   | SOUT       | High              | CPU output showing it is in an |

|      |            | <b>O</b>          | output cycle.                  |

| 46   | SINP       | High              | CPU output showing it is in an |

|      |            | <b>G</b>          | input cycle.                   |

| 47   | SMEMR      | High              | CPU status signal indicating   |

|      |            | <u> </u>          | the current cycle is a Memory  |

|      |            |                   | Read cycle.                    |

| 48   | SHLTA      | High              | CPU status signal indicating   |

|      |            | 3                 | the CPU is halted.             |

| 49   | CLOCK(2MH: | z) Low            | A buftered 2 MHz clock for     |

| -,   | •          | •                 | general use.                   |

| 50   | GND        | NA                | Ground (common)                |

| 51   | +8 Volts   | NA                | (Same as pin 1)                |

| 52   | -16 Volts  | NA                | Unregulated-16 Volts DC.       |

|      |            |                   | This voltage should not be     |

|      |            |                   | greater than -16 or less than  |

|      |            |                   | -20 Volts.                     |

| 53   | SSW DSB    | Low               | Sense Switch Disable disables  |

|      |            |                   | CPU board data input buffers   |

|      |            |                   | so that CPU can read sense     |

|      |            |                   | switches.                      |

| 54   | EXT CLR    | Low               | Front panel generated I/O      |

|      |            |                   | clear signal.                  |

| 55   |            | NA                | Not used                       |

| 56   |            | NA                | Not used                       |

| 57   |            | NA                | Not used                       |

| 58   |            | NA                | Not used                       |

| 59   |            | NA                | Not used                       |

| 60   |            | NA                | Not used                       |

| 61   |            | NA                | Not used                       |

| 62   |            | NA                | Not used                       |

| 63   |            | NA                | Not used                       |

| 64   |            | NA                | Not used                       |

| 65   |            | NA                | Not used                       |

| 66   |            | NA                | Not used                       |

| 67   | PHANTOM    | NA                | Used for Memory Bank Selection |

| 01   | Figu       | re 3B (continued) | (or for SOL Systems)           |

| Pin #     | Mnemonic       | Enabled State      | Description                                                                                                       |

|-----------|----------------|--------------------|-------------------------------------------------------------------------------------------------------------------|

| 68        | MWRITE         | High               | CPU output showing Data Out Bus data is to be written                                                             |

| 69        | <del>P</del> s | Low                | into the memory selected by<br>the address lines.<br>Shows Protect Status of                                      |

| _         |                |                    | selected memory.                                                                                                  |

| 70        | PROTECT        | High               | Combined with address in an AND gate on a memory board which causes the PROTECT flip-flop to be set.              |

| 71        | RUN            | High               | Front panel indication that CPU run instruction has been input.                                                   |

| 72        | PRDY           | Low                | Causes the CPU to enter the WAIT state when enabled.                                                              |

| 73        | PINT           | Low                | If interrupts have been en-<br>abled causes the CPU to enter<br>the Interrupt Acknowledge                         |

|           |                |                    | condition at the conclusion of the current instruction.                                                           |

| 74        | PHOLD          | Low                | CPU input which causes a                                                                                          |

|           |                |                    | HOLD status to occur. DMA transfer request signal is PHOLD.                                                       |

| 75        | PRESET         | Low                | CPU board system reset signal.                                                                                    |

| 76        | PSYNC          | High               | CPU output showing the start of a new machine cycle. This signal is used on the CPU                               |

| 77        | PWR            | Low                | board to enable the loading of the System Status Latch. Indication that data on the Data Out Bus is to be written |

| 70        | ואזממט         | Low                | either to a memory or an I/O device. Indication to the selected                                                   |

| 78        | PDBIN          | Low                | memory or I/O device that<br>the CPU expects data on the<br>Data In Bus.                                          |

| 79        | A 0            | High               | Address Bit 0                                                                                                     |

| 80        | Al             | High               | Address Bit l                                                                                                     |

| 81        | A2             | High               | Address Bit 2                                                                                                     |

| 82        | A6             | High               | Address Bit 6                                                                                                     |

| 83        | A7             | High               | Address Bit 7                                                                                                     |

| 84        | A8             | High               | Address Bit 8                                                                                                     |

| 85<br>0./ | A13            | High               | Address Bit 13<br>Address Bit 14                                                                                  |

| 86<br>87  | A14<br>A11     | High<br>High       | Address Bit 11                                                                                                    |

| 88        | DO2            | High               | CPU Data Out Bit 2                                                                                                |

| 89        | DO3            | High               | CPU Data Out Bit 3                                                                                                |

| 90        | DO7            | High               | CPU Data Out Bit 7                                                                                                |

| 91        | DI4            | High               | Data In Bit 4 to CPU                                                                                              |

| 92        | DI5            | High               | Data In Bit 5 to CPU                                                                                              |

| 93        | DI6            | High               | Data In Bit 6 to CPU                                                                                              |

|           | Fig            | ure 3B (continued) |                                                                                                                   |

S-100 (WAMECO) BUS DESCRIPTION (Cont.)

| Pin# | Mnemonic | Enabled State | Description                   |

|------|----------|---------------|-------------------------------|

| 94   | DII      | High          | Data In Bit 1 to CPU          |

| 95   | DI0      | High          | Data In Bit 0 to CPU          |

| 96   | SINTA    | High          | CPU Interrupt Acknowledge     |

| -    |          | •             | Signal                        |

| 97   | SWO      | Low           | CPU output indicating the     |

|      |          |               | current cycle involves        |

|      |          |               | writing to a memory or        |

|      |          |               | I/O device.                   |

| 98   | SSTACK   | High          | CPU output indicating the     |

|      |          | _             | address bus contains the      |

|      |          |               | stack address and the current |

|      |          |               | cycle will have a stack       |

|      |          |               | operation.                    |

| 99   | POC      | Low           | Power On Clear reset signal   |

| 100  | GND      | NA            | Ground (common)               |

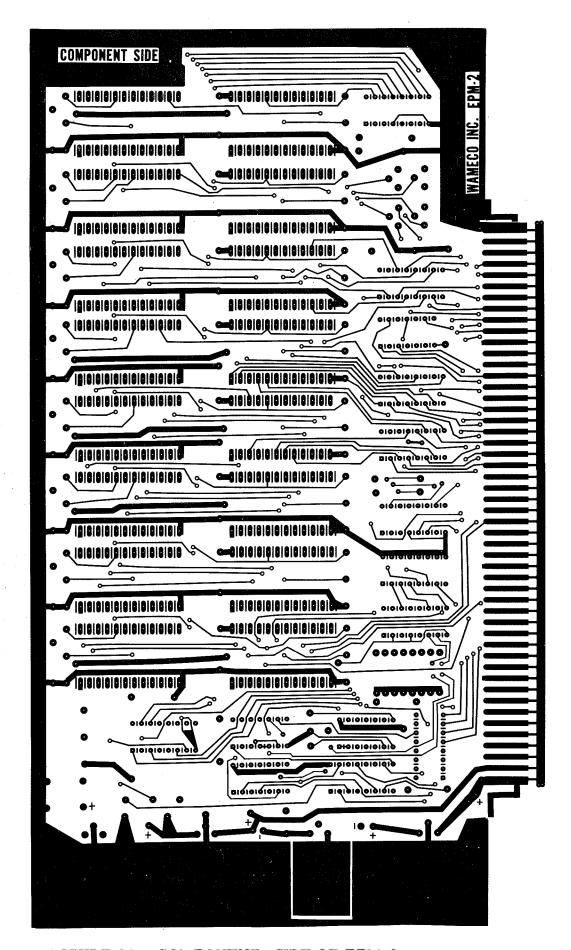

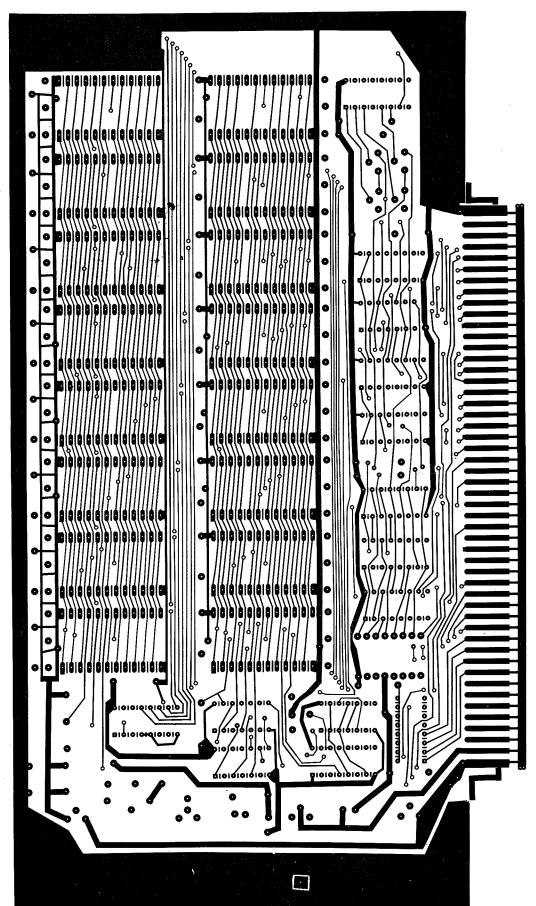

#### I. Assembly of EPM-2

- I-1. Before placing any parts on the board, check the board for any hairline shorts (slivers). All boards have been inspected at least three times before shipping. Still, a good hobbyist checks any board he buys.

- I-2. Using a strong light and a magnifying glass, very carefully check all leads on the top of the board (this is the side marked COMPONENT SIDE). If any slivers are found, carefully cut and scrape them with an XACTO knife. The underside of the board will be checked after assembly.

- I-3. Place all the 14, 16, and 24 pin sockets in their positions on the top side of the board.

- I-4. After positioning all the sockets in place, check to ensure that a socket is not in the position S1 or S2. Dip switches will not stay in place in a socket. Place a book on top of the sockets, hold the book tight against the board and turn them over so that the underside of the board is up. Press down on the board and solder one pin on each end of each socket. This will ensure the sockets are flat against the board. When the tacking of all sockets is completed, finish soldering all the other pins of the sockets.

#### NOTE

DO NOT PUT IC'S IN SOCKETS AT THIS TIME. THEY WILL BE INSTALLED LATER.

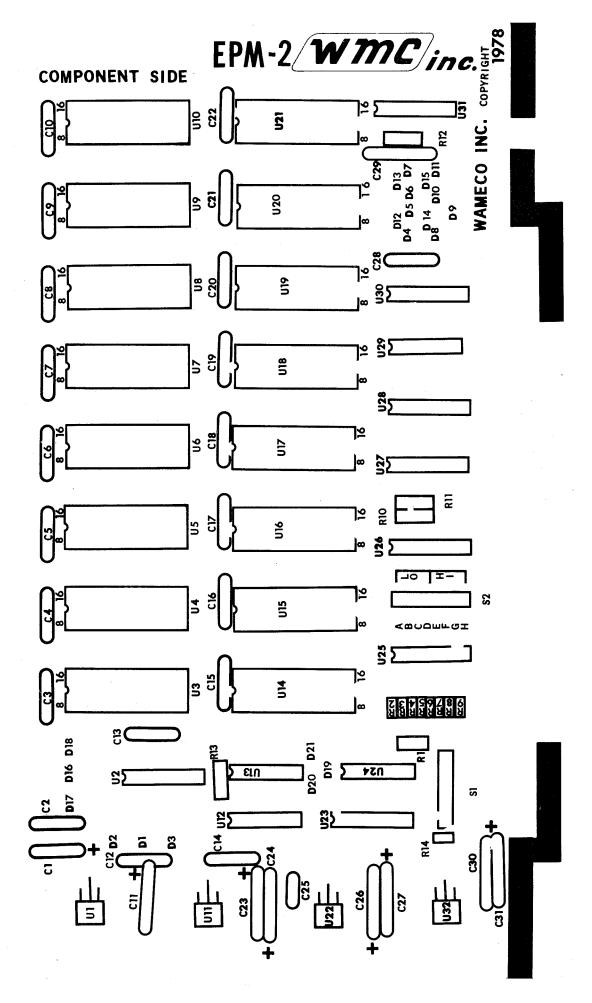

- I-5. Bend the leads on all the resistors (2.7K $\Omega$  RED, VIOLET, RED) and place in board. Check parts placement drawing (figure 3) for correct locations. Bend the leads of the resistors on the underside of the board to retain them in place until they are soldered. Turn the board over and solder all the resistors. Clip the leads of the resistors flush with the underside of the board with the diagonal pliers.

- I-6. Put the leads of C2-C10, C12-C22, C25, C28-C30 (.1  $\mu$ F) disc capacitors in the board. Check parts placement drawing (figure 3) for proper locations. Bend the leads of the capacitors to retain them in place until they are soldered. Turn the board over and solder the capacitors. Clip the leads of the capacitors flush with the underside of the board with the diagonal pliers.

- I-7. Place C1, C11, C23, C24, C26, C27, C31 (22  $\mu$ F tantalum) in place. Ensure that the polarities are correct. Check parts placement drawing (figure 3) for correct placement and polarity. Bend the leads of the capacitors to retain them in place until they are soldered. Turn the board over and rest it on books. Solder the capacitors in place. Clip the leads flush with the underside of the board with diagonal pliers.

- I-8. Put the eight position dip switches in place. Ensure that switch S1 is installed so that the OFF position is towards the gold fingers of the board and switch S2 is installed so that the OFF position is toward the voltage regulators. Bend the two pins at each end of each switch to retain it in place until it is soldered. Turn the board over and rest it on books as before. Solder the eight position dip switches in place.

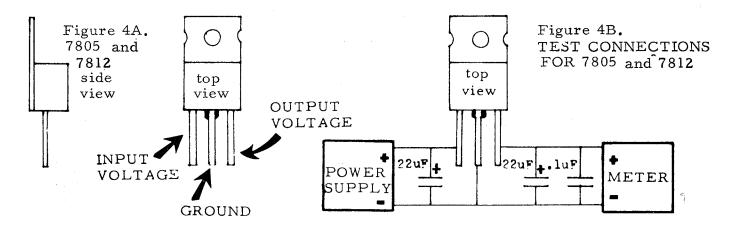

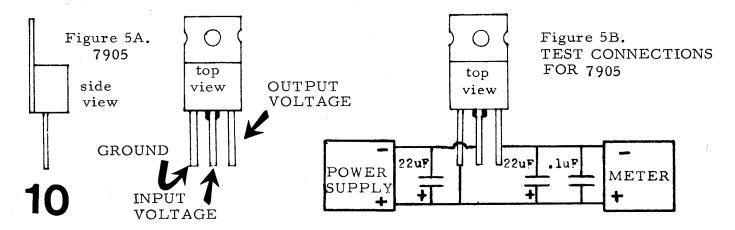

I-9. Before installing the regulators, it is recommended that they be tested for proper voltage regulation.

To prevent oscillation of the regulators, assemble a test rig as shown. The capacitors must be installed ovserving the correct polarity. This test rig is for pre-installation testing only. The filter capacitors installed on the board serve the same purpose in the final assembly. Attach the power supply, multimeter, and capacitors to the 7805 as shown in figure 4B. Place the multimeter in a DC range that will allow 10 volts to be displayed. The regulator needs a 2.0 volt minimum difference between the input voltage and the regulated output voltage. If the power supply has a voltmeter, observe the input voltage during the test using that. If the power supply does not have a voltmeter, switch the + meter lead between the input lead and output lead. The input and output voltages can this be observed.

- I-10. Slowly increase the input voltage and observe the input and output voltages. When the input voltage is between 7.0 and 7.5 volts, the regulated output of a properly operating 7805 should be between 4.8 and 5.2 volts. Replace the regulator if it does not meet these limits.

- I-11. Attach the power supply, multimeter, and capacitors to the 7812 as shown in figure 4B. Place the multimeter in a DC range that will allow 15 volts to be displayed. The regulator needs a 2.0 volt minimum difference between the input voltage and the regulated output voltage.

- I-12. Slowly increase the input voltage and observe the input and output voltages. When the input is between 14.0 and 14.5 volts, the regulated output of a properly operating 7812 is between 11.8 and 12.2 volts. Replace the regulator if it does not meet these limits.

- I-13. Attach the power supply, multimeter, and capacitors to the 7905 as shown in figure 5B. Place the multimeter in a DC range that will allow 10 volts to be displayed. The 7905 needs a 2.0 volt minimum difference between the input and regulated output to work properly. If the power supply does not have a voltmeter, switch the meter lead between the output and the input lead of the regulator during the test.

- I-14. Slowly increase the input voltage and observe the input and output voltages. When the input voltage is between 7.0 and 7.5 volts, the regulated output of a properly operating 7905 should be between 4.5 and 5.5 volts. Replace the regulator if it does not meet these limits.

- I-15. When the regulators have been tested as outlined in I-10 through I-14, place the regulators on the board so that the mounting hole of the regulator lines up with the corresponding hole of the EPM-2. Check the parts placement drawing (figure 3) for correct placement of the regulator. Note where the leads of the regulator pass over the connection holes on the EPM-2. Bend the leads of the regulator so that the leads can be inserted into the proper holes. Mount the regulator on the board using a #6 nut and a 5/8" 6-30 screw. Insert a heatsink between the board and the regulator. Solder the leads of the regulator in place.

- I-16. Remove the nut and screw from the regulator. Bend the regulator upward and remove the heatsink. Place a moderate amount of thermal compound on the underside of the regulator and heatsink with a cotton swab. Coat all of the area mentioned with an even layer of the thermal compound, reinstall the heatsink, nut and screw. On the 7905's install the insulating washer to isolate the -15V input from ground. Ensure the nut is tight.

- I-17. Clean off the flux on the underside of the board with flux cleaner.

#### II. Inspection and Testing

II-1. Use a bright light and magnifying glass to inspect all the traces on the underside of the board. If any slivers are found, cut and scrape them with an XACTO knife. Use the solder wick and soldering iron to remove any solder bridges found. Cover the solder bridge with flux and place a clean piece of solder wick on top of the bridge. Place the soldering iron on top of the solder wick and hold until solder is seen flowing up into the solder wick. Remove the iron and wick. Check to see if the bridge has has been completely removed. If not, repeat the process until the bridge has been removed. Clean the flux off the board with flux cleaner.

## NOTE

AT THIS TIME, NO IC'S HAVE BEEN INSTALLED ON THE BOARD. DO NOT INSTALL IC'S ON THE BOARD UNTIL CALLED FOR IN THE CHECK OUT PROCEDURE.

II-2. Place the multimeter in the R x l scale. Place one probe on the gold finger for pin 1. Place the other probe sequentially on all the other fingers to check for shorts. Repeat this procedure for each pin. There should be only two sets of pins that are shorted; l to 5l and 50 to 100. If any other pair of pins are shorted, use a strong light and magnifying glass to locate the solder bridge or silver causing

the short. When the short has been located, correct it as outlined in II-1. If there is no solder bridge or sliver, a component is shorted. Check the EPM-2 schematic (figure 6) to locate the probable component. Lift one lead of the suspected component and recheck between the two fingers that had a bad reading. If the bad reading is now correct, replace the component. If the reading is still bad, continue troubleshooting until the faulty component is located and replaced. Ensure that all components that had a lead lifted have the lead reconnected.

WARNING

DO NOT INSTALL OR REMOVE ANY BOARD IN COMPUTER WITH POWER ON. DAMAGE TO BOARDS AND COMPUTER MAY RESULT.

- II-3. Ensure computer is OFF. Plug EPM-2 into the motherboard. Check that the EPM-2 is correctly plugged in and that the board is fully seated in the connector. Turn the computer power ON and check the outputs of each regulator on the EPM-2. If the regulators do not have output voltages as stated in I-10, I-12, and I-14, turn the computer power OFF and replace the defective regulator. Repeat I-10, I-12, or I-14 as appropriate to check out the new regulator before installing. If the voltage on the regulators are not correct now, check the voltages on the motherboard. If the voltages on the motherboard are incorrect, repair the power supply as needed. If and when the voltages check good, turn the computer power OFF and remove the EPM-2 from the motherboard.

- II-4. Select the proper wait state and EPROM configuration on the board by installing the jumpers on the EPM-2 as shown in table III.

- II-5. Clean off the flux on the underside of the board with flux cleaner.

- II-6. Install all the IC's on the EPM-2. Check parts placement drawing (figure 3) for proper location and correct polarity of IC's.

# CAUTION

ENSURE ALL IC'S ARE INSTALLED CORRECTLY. INCORRECT POLARIZATION OF IC WILL RESULT IN DAMAGE TO IC AND CAUSE SUBSEQUENT TROUBLES TO APPEAR ON THE BOARD.

- II-7. The address range of the EPM-2 is set by the start and stop address selected on S2. The minimum range is 4 K Bytes. Select the address range desired using the memory address range select portion of Table III.

- II-8. The EPM-2 may be populated one EPROM at a time. The lowest memory address on the board is the top left hand chip U3. The address range increases to the right. The lower row of EPROMs are the higher addresses and also increase to the right. The highest address chip is U21.

13

# TABLE III. EPM-2 BOARD CONFIGURATION JUMPER SELECTION

| Wait states | Connect D22 to |

|-------------|----------------|

| Ø           | D19            |

| 1           | D20            |

| 2           | D21            |

# NOTE

U24 NEED NOT BE INSTALLED IF THE "NO WAIT" SELECTION IS MADE

#### 2708 - 16 K BYTE CONFIGURATION

| connect | to                          |

|---------|-----------------------------|

| D1      | D3                          |

| D4      | D1 <b>2</b>                 |

| D6      | D13                         |

| D8      | D 14                        |

| D10     | D15                         |

| D16     | D17                         |

| Pin 18  | Ground at each ROM location |

# 2716 -32K BYTE CONFIGURATION

| connect | to                          |

|---------|-----------------------------|

| D1      | D2                          |

| D5      | D12                         |

| D7      | D13                         |

| D9      | D14                         |

| D11     | D15                         |

| D16     | D18                         |

| Pin 18  | Pin 20 at each ROM location |

#### MEMORY ADDRESS RANGE SELECT -

| HIGH LIMIT                                                                    | <u>:</u>                                                     | LOW LI | MIT                                                     |                                        | Address R | ange                                                                                         |

|-------------------------------------------------------------------------------|--------------------------------------------------------------|--------|---------------------------------------------------------|----------------------------------------|-----------|----------------------------------------------------------------------------------------------|

| A B C                                                                         | DE                                                           | F      | G                                                       | H                                      |           |                                                                                              |

| OFF OFF OFF OFF OFF OFF OFF ON OFF ON ON OFF ON OFF ON ON ON ON ON ON OFF OFF | OFF OFF OFF ON OFF ON OFF ON OFF ON OFF ON ON ON ON ON ON ON | OFF    | OFF<br>OFF<br>ON<br>ON<br>OFF<br>ON<br>OFF<br>OFF<br>ON | OFF ON OFF ON OFF ON OFF ON OFF ON OFF |           | 0FFF<br>1FFF<br>2FFF<br>3FFF<br>4FFF<br>5FFF<br>6FFF<br>7FFF<br>8FFF<br>9FFF<br>AFFF<br>BFFF |

| ON ON OFF                                                                     | OFF ON                                                       | ON     | OFF                                                     | OFF                                    | C000      | CFFF                                                                                         |

| ON ON OFF                                                                     | ON ON                                                        | ON     | OFF                                                     | ON                                     | D000      | DFFF                                                                                         |

| ON ON ON                                                                      | OFF ON                                                       | ON     | ON                                                      | OFF                                    | E000      | EFFF                                                                                         |

| ON ON ON                                                                      | ON ON                                                        | on     | on                                                      | ON                                     | F000      | FFFF                                                                                         |

#### TABLE III EPM-2 BOARD CONFIGURATION CONT.

#### ADDRESS SELECT REQUIREMENT:

Low Limit Setting

Desired Address Range

High Limit Setting

## NOTE

IT IS RECOMMENDED THAT TAPE BE APPLIED OVER THE ERASE WINDOWS OF THE EPROM'S AFTER THEY ARE PROGRAMMED. THERE HAVE BEEN CASES WHERE A GRADUAL ERASURE OCCURRED BECAUSE OF EXPOSURE TO ORDINARY LIGHT.

II-9. Program the EPROM with the program given in figure 7. Install the EPROM in the first location to be tested (U3). The program given for the EPROM will sequentually check all the address and data access lines for the location that the EPROM is inserted in.

# NOTE

FIGURE 7 DOES NOT CONTAIN THE COMPLETE PROGRAM. EVERY 256 LOCATIONS, THE SOURCE STATEMENTS ARE LOOPED. AT SEQUENCE 293, DB ØSTARTED AND IS INCREMENTED EACH SEQUENCE UP TO SEQUENCE 548 WHICH IS DB 255. THIS IS REPEATED UNTIL ALL THE MEMORY LOCATIONS OF THE EPROM ARE PROGRAMMED.

- II-10. Ensure the computer is OFF. Plug the EPM-2 into the motherboard. Check that the EPM-2 is correctly plugged in and that the board is fully seated in the connector.

- II-11. Set the address of the RAM board to 00000. Plug the RAM board into the motherboard. Check that the RAM board is correctly plugged in and that the board is fully seated in the connector.

# NOTE

WHEN POWER IS APPLIED TO AN 8080 SYSTEM, THE MICROPROCESSOR DOES NOT COME UP IN ANY DETERMINABLE MODE. TO CORRECTLY INITIALIZE THE COMPUTER, HOLD THE STOP SWITCH IN STOP AND PUSH THE RESET TO RESET.

- II-12. Turn the computer ON. Set the starting address of the EPROM board into the computer and select EXAMINE.

- II-13. Enter the most significant Byte of the start address into the data switches (port FF).

- II-14. Select RUN. The program will loop at 0H if the test is good.

| LOC                          | OBJ                  | SEQ            | SOURCE STATE                    | MENT                                  |

|------------------------------|----------------------|----------------|---------------------------------|---------------------------------------|

| 0000<br>0003                 | 210000<br>36C3       | 1<br>2<br>3    | CSEG<br>LXI H, 0<br>MVI M, 0C3H | ;JMP TO ZERO, GOOD TEST               |

| 0005                         | 23                   | 4              | INX H                           |                                       |

| 0006                         | AF                   | 5              | XRA A                           |                                       |

| 0007                         | 77                   | 6              | MOV M, A                        |                                       |

| 0008                         | 23                   | 7              | INX H                           | ;ERROR ADDRESS                        |

| 0009                         | 77                   | 8              | MOV M, A                        |                                       |

| 000A                         | 210800               | 9              | LXI H, 8                        |                                       |

| 000D                         | 36C3                 | 10             | MVI M, 0C3H                     |                                       |

| 000F                         | 23                   | 11             | INX H                           |                                       |

| 0010                         | 3608                 | 12             | MVI M, 8                        |                                       |

| 0012                         | 23                   | 13             | INX H                           |                                       |

| 0012<br>0013<br>0014<br>0016 | 77<br>DBFF<br>67     | 14<br>15<br>16 | MOV M, A<br>IN 0FFH<br>MOV H, A | GET START OF MEM TEST                 |

| 0017                         | C604                 | 17             | ADI 4                           | ;SAVE END OF TEST ADDRESS             |

| 0019                         | 3 <b>222</b> 00      | 18             | STA 22H                         |                                       |

| 001C                         | <b>2</b> E26         | 19             | MVI L, 26H                      |                                       |

| 001E<br>0021<br>0023         | 222000<br>0600<br>EB | 20<br>21<br>22 | SHLD 20H<br>MVI B, 1<br>XCHG    | ;SAVE IT<br>;CLEAR COUNTER            |

| 0024                         | 1E3D                 | 23             | MVI E, 3DH                      |                                       |

| 0026                         | 1A                   | 24 LOOP:       | LDAX D                          |                                       |

| 0027                         | EB                   | 25             | XCHG                            |                                       |

| 0028                         | 223000               | 26             | SHLD 30H                        |                                       |

| 002B                         | EB                   | 27             | XCHG                            | ;DOESNT COMPARE, ERROR                |

| 002C                         | B8                   | 28             | CMP B                           |                                       |

| 002D                         | C20800               | 29             | JNZ 8                           |                                       |

| 0030                         | 13                   | 30             | INX D                           | · · · · · · · · · · · · · · · · · · · |

| 0031                         | 04                   | 31             | INR B                           |                                       |

| 0032                         | 3A2200               | 32             | LDA 22H                         |                                       |

| 0035                         | BA                   | 33             | CMP D                           | ;DONE, ALL OK!                        |

| 0036                         | CA0000               | 34             | JZ 0                            |                                       |

| 0039                         | 2A2000               | 35             | LHLD 20H                        |                                       |

| 003C<br>003D                 | E9                   | 36<br>37<br>38 | PCHL DB 1                       | ;LOOP BACK                            |

| 003E                         | 02                   | 39             | DB 2                            |                                       |

| 003F                         | 03                   | 40             | DB 3                            |                                       |

| 0040                         | 04                   | 41             | DB 4                            |                                       |

| 0041                         | 05                   | 42             | DB 5                            |                                       |

| 0042<br>0043<br>0044         | 06<br>07<br>08       | 43<br>44<br>45 | DB 6 DB 7 DB 8                  |                                       |

| 0045                         | 09                   | 46             | DB 9                            |                                       |

| 0046                         | 0A                   | 47             | DB 10                           |                                       |

| 0047                         | 0B                   | 48             | DB 11                           |                                       |

| 0048                         | 0C                   | 49             | DB 12                           |                                       |

| 0049                         | 0D                   | 50             | DB 13                           |                                       |

| 004A                         | 0E                   | 51             | DB 14                           |                                       |

| 004B                         | 0F                   | 52             | DB 15                           |                                       |

| L00          | 0BJ  | SEQ.           | SOURCE STATEMENT | LOC 08 <i>1</i>     | SEQ        | Source Statement |

|--------------|------|----------------|------------------|---------------------|------------|------------------|

| 004C         | 10   | 53             | DB 16            | 0083 47             | 108        | 08 71            |

| 0040         |      | 54             | DB 17            | 0084 48             | 109        | DB 72            |

| 004E         |      | 55             | DB 18            | 0085 49             | 110        | DB 73            |

| 004F         |      | 56             | DB 19            | 0086 4A             | 111        | DB 74            |

| 0050         |      | 57             | DB 20            | 0087 4 <del>8</del> | 112        | DB 75            |

| 0051         |      | 58             | 08 21            | 0088 4C             | 113        | DB 76            |

| 0052         |      | 59             | DB 22            | 0089 4D             | 114        | 0B 77            |

| 0053         | 17   | 60             | OB 23            | 008A 4E             | 115        | DB 78            |

| 0054         |      | 61             | DB 24            | 008B 4F             | 116        | DB 79            |

| 0055         | 19   | <del>6</del> 2 | DB 25            | 008C 50             | 117        | DB 80            |

| 9956         | 18   | 63             | DB 26            | 008D 51             | 118        | DB 81            |

| 0057         | 18   | 64             | DB 27            | 008E 52             | 119        | DB 82            |

| 0058         | 10   | 65             | DB 28            | 008F 53             | 120        | DB 83            |

| 0059         | 1D   | 66             | 0B, 29           | 0090 54             | 121        | DB 84            |

| 005A         |      | 67             | DB 30            | 0091 55             | 122        | DB 85            |

| 005B         |      | 68             | DB 3i            | 0092 56             | 123        | DB 86            |

| <b>005</b> 0 |      | <del>69</del>  | DB 32            | 0093 57             | 124        | DB 87            |

| 005D         |      | 70             | DB 33            | 0094 58             | 125        | DB 88            |

| 005E         |      | 71             | DB 34            | 0095 59             | 126        | DB 89            |

| 005F         |      | 72             | DB 35            | 0096 5A             | 127        | DB 90            |

| 0060         |      | 73             | DB 36            | 0097 5B             | 128        | 08 91            |

| 0061         |      | . 74           | DB 37            | 0098 5C             | 129        | DB 92            |

| 0062         |      | 75<br>         | DB 38            | 0099 5D             | 130        | DB 93            |

| 0063         |      | 76<br>         | 08 39            | 009A 5E             | 131<br>430 | DB 94            |

| 0064         |      | 77             | CB 40            | 009B 5F             | 132        | 08 95<br>no ac   |

| 0065         |      | 78             | DB 41            | 009C 60             | 133<br>474 | DB 96            |

| 0066         |      | 79             | DB 42            | 009D 61<br>009E 62  | 134<br>135 | DB 97<br>DB 98   |

| 9967         |      | .88<br>        | 0B 43            | 009F 63             | 136        | DB 99            |

| 0068<br>8868 |      | 81             | DB 44<br>DB 45   | 009A 63             | 137        | DB 100           |

| 0069<br>006A |      | 82<br>83       | 06 45<br>08 46   | 00A1 65             | 138        | DB 101           |

| 006B         |      | 84             | 08 47            | 00A2 66             | 139        | DB 102           |

| 0060<br>0060 |      | 8 <del>5</del> | DB 48            | 00A3 67             | 140        | DB 103           |

| 006D         |      | 36<br>86       | DB 49            | 00A4 68             | 141        | DB 104           |

| 006E         |      | 87             | DB 50            | 00A5 69             | 142        | DB 105           |

| 996F         |      | 88             | DB 51            | 00A6 6A             | 143        | DB 106           |

| 0070         |      | 89             | DB 52            | 00A7 6B             | 144        | DB 107           |

| 0071         |      | <br>90         | DB 53            | 00A8 60             | 145        | DB 108           |

| 0072         |      | 91             | DB 54            | 00A9 6D             | 146        | DB 109           |

| 0073         |      | 92             | DB 55            | 00AA 6E             | 147        | DB 110           |

| 0074         |      | 93             | DB 56            | 00AB 6F             | 148        | DB 111           |

| 0075         | 39   | 94             | DB 57            | 00AC 70             | 149        | DB 112           |

| 0076         | 3A   | 95             | DB 58            | 00AD 71             | 150        | DB 113           |

| 0077         | ' 3B | 96             | DB 59            | 00AE 72             | 151        | DB 114           |

| 0078         | 30   | 97             | DB 60            | 00AF 73             | 152        | DB 115           |

| 0075         |      | 98             | DB 61            | 00B0 74             | 153        | DB 116           |

| 007F         |      | 99             | DB 62            | 00B1 75             | 154        | DB 117           |

| 007E         |      | 100            | DB 63            | 00B2 76             | 155        | DB 118           |

| 0070         |      | 101            | DB 64            | 00B3 77             | 156        | DB 119           |

| 9970         |      | 102            | DB 65            | 00B4 78             | 157        | DB 120           |

| 007E         |      | 103            | DB 66            | 00B5 79             | 158        | DB 121           |

| 007F         |      | 104            | DB 67            | 0086 7A             | 159        | DB 122           |

| 0080         |      | 105            | DB 68            | 00B7 7B             | 160        | DB 123           |

| 0081         |      | 106            | DB 69            | 00B8 7C             | 161<br>470 | DB 124           |

| 0083         | 2 46 | 107            | DB 70            | 00 <b>B</b> 9 70    | 162        | DB 125           |

| LOC          | 0BJ  | 5EQ         | SOURCE STATEMENT | LOC OBJ | SEQ.       | SOURCE STATEMENT |

|--------------|------|-------------|------------------|---------|------------|------------------|

| 90EA         |      | 163         | DB 126           | 00F1 B5 | 218        | DB 181           |

| 99BB         | 7F   | 164         | 98 127           | 00F2 B6 | 219        | DB 182           |

| 00BC         | 80   | 165         | 08 128           | 00F3 B7 | 220        | DB 183           |

| 00BD         | 81   | 166         | D8 129           | 00F4 B8 | 221        | DB 184           |

| 00BE         | 82   | 167         | 08 130           | 00F5 B9 | 222        | DB 185           |

| 00BF         | 83   | 168         | DB 131           | 00F6 BA | 223        | DB 186           |

| 00C0         | 84   | 169         | DB 132           | 00F7 BB | 224        | DB 187           |

| 0001         |      | 170         | DB 133           | 00F8 BC | 225        | DB 188           |

| 00C2         |      | 171         | DB 134           | 00F9 BD | 226        | DB 189           |

| 00C3         |      | 172         | DB 135           | 00FA BE | 227        | DB 190           |

| 00C4         |      | 173         | DB 136           | 00FB BF | 228        | DB 191           |

| 00C5         |      | 174         | DB 137           | 00FC C0 | 229        | DB 192           |

| 0006         |      | 175         | DB 138           | 00FD C1 | 230<br>230 | DB 193           |

| 0007         |      | 176         | DB 139           | 00FE C2 | 231        | DB 194           |

| 99C8         |      | 177         | DB 140           | 00FF C3 |            | DB 195           |

| 00C9         |      | 178         | DB 141           | 0100 C4 | 232        |                  |

| 00CA         |      | 179         | DB 142           |         | 233        | DB 196           |

| 00CB         |      |             |                  | 0101 05 | 234        | DB 197           |

| 00CC         |      | 180         | DB 143           | 0102 C6 | 235        | DB 198           |

|              |      | 181         | DB 144           | 0103 C7 | 236        | DB 199           |

| 00CD         |      | 182         | DB 145           | 0104 C8 | 237        | DB 200           |

| 00CE         |      | 183         | DB 146           | 0105 C9 | 238        | DB 201           |

| 00CF         |      | 184         | DB 147           | 0106 CA | 239        | DB 202           |

| 00D0         |      | 185         | DB 148           | 0107 CB | 240        | DB 203           |

| 00D1         |      | 186         | DB 149           | 0108 CC | 241        | DB 204           |

| 00D2         |      | 187         | DB 150           | 0109 CD | 242        | DB 205           |

| <b>00D</b> 3 |      | 188         | DB 151           | 010A CE | 243        | DB 206           |

| 00D4         |      | 189         | DB 152           | 010B CF | 244        | DB 207           |

| 00D5         |      | 190         | DB 153           | 010C D0 | 245        | DB 208           |

| 00D6         |      | 191         | DB 154           | 010D D1 | 246        | DB 209           |

| 00D7         |      | 192         | 08 155           | 010E D2 | 247        | DB 210           |

| 00D8         | 90   | <b>19</b> 3 | DB 156           | 010F D3 | 248        | DB 211           |

| 00D9         | 90   | 194         | DB 157           | 0110 D4 | 249        | DB 212           |

| 00DA         | 9E   | 195         | DB 158           | 0111 D5 | 250        | DB 213           |

| 00DB         | 9F   | 196         | DB 159           | 0112 D6 | 251        | DB 214           |

| 00DC         | A0   | 197         | DB 160           | 0113 D7 | 252        | DB 215           |

| 00DD         | A1   | 198         | DB 161           | 0114 D8 | 253        | DB 216           |

| 00DE         |      | 199         | DB 162           | 0115 D9 | 254        | DB 217           |

| 00DF         | A3 - | 200         | DB 163           | 0116 DA | 255        | DB 218           |

| 00E0         |      | 201         | DB 164           | 0117 DB | 256        | DB 219           |

| 00E1         |      | 202         | DB 165           | 0118 DC | 257        | DB 220           |

| 00E2         |      | 203         | DB 166           | 0119 DD | 258        | DB 221           |

| 00E3         |      | 204         | DB 167           | 011A DE | 259        | DB 222           |

| 00E4         |      | 205         | DB 168           | 011B DF | 260        | DB 223           |

| 90E5         |      | 206         | DB 169           | 011C E0 | 261        | DB 224           |

| 00E6         |      | 207         | DB 170           | 0110 E1 | 262        | DB 225           |

| 00E7         |      | 208         | DB 171           | 011E E2 | 263        | DB 226           |

| 00E8         |      | 209         | DB 172           | 011F E3 |            |                  |

| 00E9         |      | 210         | DB 173           | 0120 E4 | 264<br>265 | DB 227           |

| 00E3         |      | 210         | DB 174           |         | 265<br>266 | DB 228           |

| 00EB         |      | 212         |                  | 0121 E5 | 266        | DB 229           |

|              |      |             | DB 175           | 0122 E6 | 267        | DB 230           |

| 00EC<br>aaen |      | 213         | DB 176           | 0123 E7 | 268        | DB 231           |

| 00ED         |      | 214         | DB 177           | 0124 E8 | 269        | DB 232           |

| . 00EE .     |      | 215         | DB 178           | 0125 E9 | 270        | OB 233           |

| 00EF         |      | 216         | DB 179           | 0126 EA | 271        | DB 234           |

| 00F0         | Б4   | 217         | DB 180           | 0127 EB | 272        | DB 235           |

| *            |      |            |                  |   |   |              |     |                            |                   |

|--------------|------|------------|------------------|---|---|--------------|-----|----------------------------|-------------------|

| LOC          | QBJ  | SEQ.       | SOURCE STATEMENT |   |   | L00          | 983 | SEQ                        | SOURCE STATEMENT  |

| 9128         | Er-  | 273        | DB 236           |   |   | 015F         | 27  | 328                        | DB 35             |

| 0120         |      | 273<br>274 | 98 237           |   |   | 0160         |     | 329                        | DB 36             |

|              |      |            |                  |   |   | 9161         |     | 320<br>330                 | 08 37             |

| 012A         |      | 275<br>276 | DB 238           |   |   | 0162         |     |                            |                   |

| 012B         |      | 276        | DB 239           |   |   |              |     | 331                        | 08 38             |

| 0120         |      | 277        | DB 240           |   |   | 0163         |     | 332                        | 08 39             |

| 012D         |      | 278        | D8 241           |   |   | 0164         |     | 333                        | DB 40             |

| 012E         |      | 279        | DB 242           |   |   | 0165         |     | 334                        | DB 41             |

| 012F         |      | 280        | DB 243           |   |   | 0156         |     | 335                        | DB 42             |

| 0130         |      | 281        | DB 244           |   |   | 0167         |     | 336                        | DB 43             |

| 0131         |      | 282        | DB 245           |   |   | 9168         |     | 337                        | DB 44             |

| 0132         | F6   | 283        | DB 246           |   |   | 0169         |     | 338                        | DB 45             |

| 0133         | F7   | 284        | DB 247           |   |   | 016A         |     | 33 <b>9</b>                | DB 46             |

| 0134         | F8   | 285        | DB 248           |   |   | 0168         | 2F  | 340                        | DB 47             |

| 0135         | F9   | 286        | DB 249           |   |   | 0160         | 30  | 341                        | DB 48             |

| 0136         | FA   | 287        | DB 250           |   |   | 016D         | 31  | 342                        | DB 49             |

| 0137         | FB   | 288        | DB 251           |   |   | 016E         | 32  | 343                        | 08 50             |

| 0138         |      | 289        | DB 252           |   |   | 016F         | 33  | 344                        | 08 51             |

| 0139         |      | 290        | DB 253           |   |   | 0170         |     | 345                        | DB 52             |

| 013A         |      | 291        | DB 254           |   |   | 0171         |     | 346                        | DB 53             |

| 013B         |      | 292        | DB 255           |   |   | 0172         |     | 347                        | DB 54             |

| <b>01</b> 30 |      | 293        | DB 0             |   |   | 0173         |     | 348                        | DB 55             |

| 013D         |      | 294        | DB 1             |   |   | 0174         |     | 34 <b>9</b>                | DB 56             |

| 013E         |      | 295        | 08 2             |   |   | 0175         |     | 350                        | 08 57             |

| 013F         |      |            | DB 3             |   |   | 0176         |     | 35 <b>6</b><br>3 <b>51</b> | DB 58             |

| 013F<br>0140 |      | 296<br>207 | 08 4             |   |   | 0177         |     | 352                        | DB 59             |

|              |      | 297<br>200 |                  |   |   | 0178         |     | 353                        | · 08 60           |

| 0141         |      | 298        | DB 5             |   | • | 0179         |     | 354                        | DB 61             |

| 0142         |      | 299<br>200 | 08 6             | • |   | 017A         |     |                            |                   |

| 0143         |      | 300        | DB 7             |   |   |              |     | 355<br>350                 | 08-62             |