file in

/lib/systemd/system using WinSCP. BTW, Running S100_EdisonII from

Eclipse on your PC is never a problem.

Please also note the above step by step build bringing up the Edison (TEST1, etc.)

assumes a virgin Edison unit. If you are doing a second board first

"clean up" the Edison unit by reflashing the chip. I have had some strange

effects installing already programmed units (with the service running etc.)

-- have not have time to find out why.

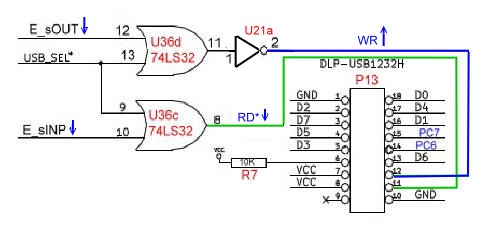

Finally the KiCAD schematic looks a little strange because I had to fool

KiCAD into connecting the SMD TXB0108's to use the same pins as the

adaptors.

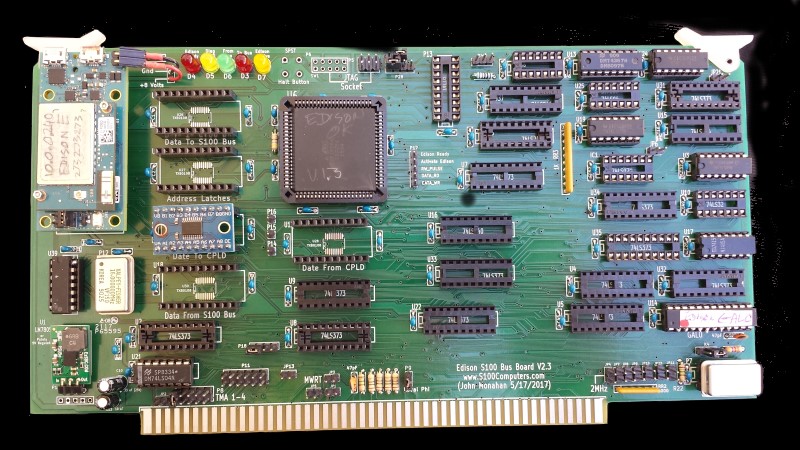

The most current version of this board is V2.3

Some time back Intel has

scrapped the Edison and some of the links to their software on the website

are all broken. The Edison boots up and you can get WiFi running, but

you cannot get the Eclipse IDE to instal as described

here.

Kipp Yeakel added the following workaround:-

To get "Intel_Edison_Setup_Win_v2016.2.007" to install the drivers I used

the

attached workaround. This gets you to step 2, updating the firmware.

This can be done manually using the iot-devkit-yp-poky-edison-20160606.zip

image because it fits on the edison partition that comes up when you attach

the USB connectors. However, if you want to install iot-devkit-prof-dev-image-edison-20160606.zip

the tool won't do this as you never get the next button enabled. I found

that this is due to the RNDIS driver

not installing. The problem is that the Intel certificate has expired. I had

to restart my computer to install unsigned drivers to get this to work.

See: https://www.maketecheasier.com/install-unsigned-drivers-windows10/ once

your computer is booted, run the edison setup program again. Do the update

firmware step pointing at your already downloaded

iot-devkit-prof-dev-image-edison-20160606.zip

file. The program will have 3 popups asking if you want to install unsigned

drivers, I said yes to all. Then the image will be written to your edison

module. I still have not gotten the next 2 steps in the setup program to

work, but it doesn't matter as you can connect via PuTTY and use the

command "configure_edison --setup"

to set the password and enable WiFi.

I was able to get the mraa library to work using

the instructions I provided above. One thing I have not figured out yet is

an easy way of setting up an IOT project. Here's what I did in windows,

1) In the right most window of eclipse there is a

"Create an IOT Project" selection. Click on it.

2) Pick Intel Edison from the next screen.

3) The next screen says Select target OS, but only

Yocto shows up, press Next.

4) Pick Intel IoT C/C++ Project and Next

5) Choose your Target, it must be powered and all the

way booted ~1minute.

6) Here is where it seems lacking... Put in a project

name "S100_Edison" for example.

7) In the drop down box pick C -> Basic -> On-Board LED

Blink

8) Click the Finish button. This will make a project

folder with all the linkages.

9) Go to your workspace folder in windows explorer.

10) Navigate to the S100_Edison/src folder.

11) Copy John's S100_Edison.c file here.

12) Edit the "C.json" file, Change the line

"main": "blink.c", to "main": "S100_Edison.c",

12) You should now be able to build the project.

13) During the build process it will prompt you for

missing or miss-matched libraries between your build environment

and the actual Edison board. Allow it to update these.

14) You should now be able to debug or run the code.